Global Wafer Level Packaging Market

Taille du marché en milliards USD

TCAC :

%

USD

10.43 Billion

USD

47.92 Billion

2025

2033

USD

10.43 Billion

USD

47.92 Billion

2025

2033

| 2026 –2033 | |

| USD 10.43 Billion | |

| USD 47.92 Billion | |

|

|

|

|

Segmentation du marché mondial du packaging au niveau de la plaquette, par intégration (dispositif passif intégré, WLP avec ventilateur intégré, WLP avec ventilateur externe et via traversant le silicium), technologie (Flip Chip, WLP conforme, boîtier à l'échelle de la puce conventionnel, boîtier à l'échelle de la plaquette au niveau de la plaquette, nano-packaging au niveau de la plaquette et packaging 3D au niveau de la plaquette), application (électronique, informatique et télécommunications, industrie, automobile, aérospatiale et défense, santé et autres), technologie de bumpage (pilier de cuivre, bumpage à la soudure, bumpage à l'or et autres) - Tendances du secteur et prévisions jusqu'en 2033

Taille du marché de l'encapsulation au niveau de la plaquette

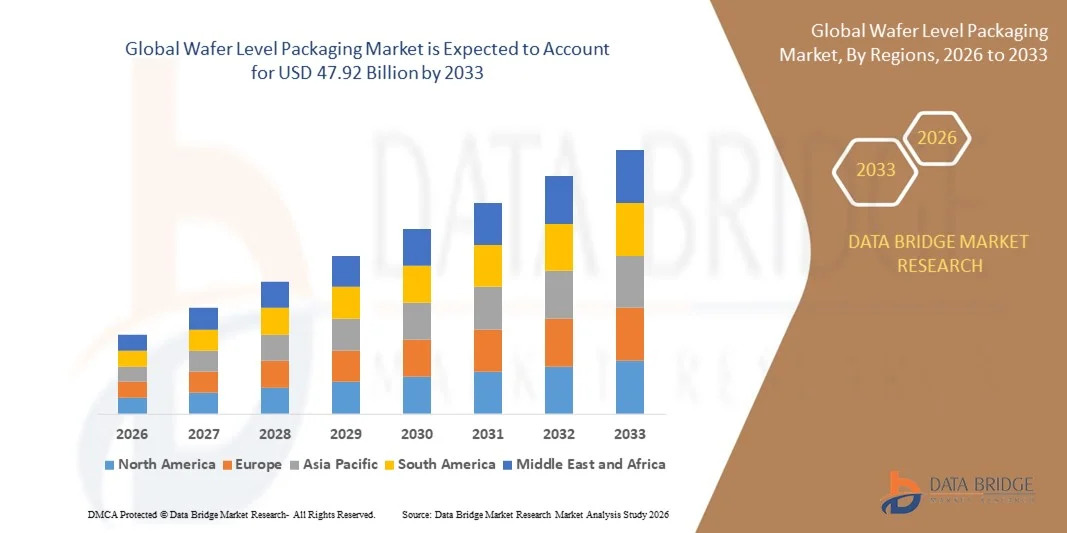

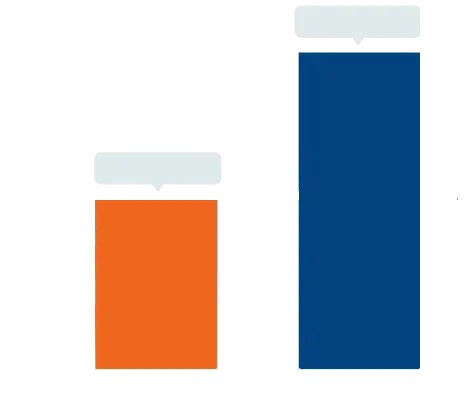

- Le marché mondial de l'encapsulation au niveau de la plaquette était évalué à 10,43 milliards de dollars en 2025 et devrait atteindre 47,92 milliards de dollars d'ici 2033 , avec un TCAC de 21,0 % au cours de la période de prévision.

- La croissance du marché est largement alimentée par la demande croissante de dispositifs semi-conducteurs compacts, performants et économes en énergie pour les applications électroniques grand public, automobiles et industrielles, incitant les fabricants à adopter des méthodes d'encapsulation avancées au niveau de la plaquette afin d'améliorer les fonctionnalités et de réduire l'encombrement.

- De plus, la production croissante de smartphones, d'objets connectés et de dispositifs IoT accélère le besoin de performances thermiques améliorées, d'une densité d'entrée/sortie plus élevée et de caractéristiques électriques supérieures, faisant de l'encapsulation au niveau de la plaquette une technologie essentielle pour les systèmes électroniques de nouvelle génération.

Analyse du marché de l'encapsulation au niveau de la plaquette

- L'encapsulation au niveau de la plaquette, qui permet l'intégration de multiples fonctions dès le stade de la plaquette, devient une technologie essentielle pour la fabrication moderne de semi-conducteurs grâce à sa capacité à offrir une miniaturisation accrue, une fiabilité améliorée et des performances électriques optimisées pour une large gamme de dispositifs finaux.

- La demande croissante d'encapsulation au niveau de la plaquette est principalement due aux progrès rapides des communications mobiles, des technologies de capteurs et de l'électronique basée sur l'IA, associés à l'évolution mondiale vers des composants semi-conducteurs plus petits, plus rapides et plus efficaces, nécessaires dans les secteurs de la consommation, de l'automobile et de l'industrie.

- La région Asie-Pacifique a dominé le marché de l'encapsulation au niveau de la plaquette avec une part de 52,5 % en 2025, grâce à la forte présence de pôles de fabrication de semi-conducteurs, à l'adoption croissante de l'encapsulation avancée dans l'électronique grand public et à l'expansion des écosystèmes de fabrication dans les principales économies.

- L'Amérique du Nord devrait être la région connaissant la croissance la plus rapide sur le marché de l'encapsulation au niveau de la plaquette au cours de la période de prévision, en raison de la demande croissante de semi-conducteurs haute performance pour l'électronique grand public, les centres de données, l'électronique automobile et les dispositifs pilotés par l'IA.

- Le segment des dispositifs passifs intégrés (IPD) a dominé le marché en 2025, grâce à son adoption croissante dans les smartphones, les objets connectés et les applications RF nécessitant des composants miniaturisés et performants. Les IPD offrent des performances électriques supérieures, une réduction des effets parasites et une intégrité du signal améliorée, ce qui les rend essentiels dans les dispositifs de communication haute fréquence. Leur capacité à intégrer de multiples fonctions passives dans un format compact favorise leur adoption massive dans l'électronique grand public et les modules sans fil. Les fabricants privilégient également les IPD car ils permettent une production en grande série à un excellent rapport coût-efficacité. L'intégration croissante de normes de communication avancées telles que la 5G stimule encore la demande de solutions WLP basées sur les IPD dans les architectures électroniques compactes.

Portée du rapport et segmentation du marché de l'encapsulation au niveau de la plaquette

|

Attributs |

Aperçu du marché de l'encapsulation au niveau de la plaquette |

|

Segments couverts |

|

|

Pays couverts |

Amérique du Nord

Europe

Asie-Pacifique

Moyen-Orient et Afrique

Amérique du Sud

|

|

Acteurs clés du marché |

|

|

Opportunités de marché |

|

|

Ensembles d'informations de données à valeur ajoutée |

Outre les informations sur les scénarios de marché tels que la valeur du marché, le taux de croissance, la segmentation, la couverture géographique et les principaux acteurs, les rapports de marché élaborés par Data Bridge Market Research comprennent également une analyse des importations et des exportations, un aperçu de la capacité de production, une analyse de la consommation de production, une analyse des tendances des prix, un scénario de changement climatique, une analyse de la chaîne d'approvisionnement, une analyse de la chaîne de valeur, un aperçu des matières premières/consommables, les critères de sélection des fournisseurs, une analyse PESTLE, une analyse de Porter et le cadre réglementaire. |

Tendances du marché de l'encapsulation au niveau de la plaquette

Adoption croissante des technologies avancées de distribution en éventail et d'encapsulation 3D au niveau de la plaquette

- Le marché de l'encapsulation au niveau de la plaquette connaît une forte évolution vers des architectures 3D et de type fan-out avancées, les fabricants privilégiant des performances accrues et une densité d'intégration plus élevée pour les semi-conducteurs de nouvelle génération. Cette tendance est impulsée par le besoin croissant de performances électriques améliorées, de formats plus fins et d'une efficacité thermique optimisée dans des applications telles que les smartphones, le calcul haute performance et l'électronique automobile.

- Par exemple, Deca Technologies a étendu ses capacités d'encapsulation en éventail pour accompagner les principaux fabricants de semi-conducteurs qui recherchent un débit plus élevé et une flexibilité de conception accrue pour les architectures de puces complexes, démontrant ainsi comment les acteurs du secteur accélèrent l'innovation grâce à des plateformes d'encapsulation en éventail évolutives.

- Les technologies de répartition en éventail et d'encapsulation 3D au niveau de la plaquette permettent des interconnexions plus courtes, une densité d'E/S plus élevée et une meilleure intégration système-dans-le-boîtier, ce qui les rend essentielles pour les processeurs avancés, les accélérateurs d'IA et les dispositifs de calcul en périphérie qui requièrent des conceptions compactes et une forte efficacité énergétique. Cette évolution est également favorisée par l'optimisation croissante des procédés de fabrication visant à améliorer les performances tout en maîtrisant les coûts.

- La demande croissante d'intégration hétérogène favorise l'adoption de ces approches WLP avancées, les fabricants de puces intégrant de multiples fonctions telles que la mémoire, la logique et les composants RF dans des boîtiers compacts. Cette tendance est également motivée par la nécessité de pallier les limites de miniaturisation des architectures 2D traditionnelles.

- Les entreprises concentrent leurs efforts sur l'expansion de leurs capacités de production et le renforcement de la R&D pour les technologies d'encapsulation de nouvelle génération, ce qui accélère l'adoption des structures fan-out et 3D dans diverses applications microélectroniques. Cette orientation transforme les attentes en matière de performance et de miniaturisation des encapsulations de semi-conducteurs.

- L'importance croissante accordée à l'obtention de fonctionnalités système plus élevées dans des formats plus compacts pousse les fabricants à adopter des technologies d'encapsulation avancées au niveau de la plaquette, confirmant ainsi la dynamique d'adoption continue de ces technologies sur les marchés de l'électronique grand public, de l'automobile et du calcul haute performance.

Dynamique du marché de l'encapsulation au niveau de la plaquette

Conducteur

Demande croissante de dispositifs semi-conducteurs miniaturisés et hautes performances

- La demande croissante des consommateurs et des industriels pour des dispositifs semi-conducteurs compacts, économes en énergie et performants favorise l'adoption massive des solutions d'encapsulation au niveau de la plaquette (WLP) dans de nombreuses applications. À mesure que les dispositifs électroniques deviennent plus petits et plus sophistiqués, la WLP offre la densité, la vitesse et la fiabilité requises pour les architectures de puces modernes.

- Par exemple, Amkor Technology continue d'élargir sa gamme de solutions d'encapsulation avancées au niveau de la plaquette afin de répondre aux besoins croissants des fabricants de smartphones et d'appareils informatiques qui exigent des profils plus fins et des performances fonctionnelles supérieures.

- La miniaturisation croissante des appareils électroniques grand public, tels que les objets connectés, les nœuds IoT et les smartphones, alimente la demande en solutions d'encapsulation capables d'offrir une densité d'E/S élevée, une intégrité du signal améliorée et une latence réduite. La technologie WLP permet d'atteindre ces objectifs en minimisant la longueur des interconnexions et en optimisant le chemin électrique au sein du boîtier de la puce.

- Les attentes croissantes en matière de faible consommation d'énergie et de fonctionnalités améliorées incitent les fabricants à adopter l'encapsulation au niveau de la plaquette comme solution d'intégration privilégiée pour les applications grand public et industrielles. Ceci renforce son rôle crucial dans le développement des semi-conducteurs de nouvelle génération.

- La forte demande en calcul haute performance et en électronique compacte continue de positionner le WLP comme une technologie essentielle, concluant ainsi ce facteur par son importance dans la miniaturisation des puces et les progrès en matière de performances.

Retenue/Défi

Investissements en capital élevés et exigences de fabrication complexes

- Le marché de l'encapsulation au niveau de la plaquette (WLP) est confronté à des défis importants liés aux investissements considérables requis pour les infrastructures de fabrication avancées et à la complexité des procédés de production associés. La mise en place de lignes de fabrication WLP exige des équipements coûteux, des outils de précision et des environnements de salles blanches spécialisés, ce qui constitue un frein pour les nouveaux entrants et les acteurs de plus petite taille.

- Par exemple, les entreprises qui investissent dans des outils de lithographie, de collage et de métrologie de pointe doivent faire face à des engagements financiers importants, ce qui peut limiter leur capacité à augmenter rapidement leurs capacités de production. Les procédés WLP avancés, tels que le fan-out, l'empilement 3D et l'intégration hétérogène, nécessitent une expertise pointue en fabrication, un alignement précis et des techniques de manutention des matériaux avancées, ce qui accroît la complexité opérationnelle. Ces exigences font de l'optimisation des procédés un défi majeur pour de nombreuses usines d'encapsulation de semi-conducteurs.

- La nécessité d'investir continuellement dans la R&D, l'automatisation des processus et l'assurance qualité accentue la pression sur les coûts, d'autant plus que les technologies d'emballage évoluent pour prendre en charge des niveaux d'intégration plus élevés et des dimensions plus fines. Cette complexité freine l'adoption par les fabricants sensibles aux coûts.

- Avec les progrès des technologies de production, le maintien de la stabilité des rendements et de l'uniformité des processus devient de plus en plus difficile en raison de la multiplication des étapes de fabrication et des risques accrus de défauts, ce qui contribue aux difficultés opérationnelles. Ces problèmes affectent la capacité de production à grande échelle et la rentabilité.

- La combinaison d'exigences élevées en matière d'investissements initiaux et de processus de fabrication complexes constitue un défi permanent pour une adoption plus large, ce qui conclut cette section en soulignant l'importance de prendre en compte les contraintes de coût, de capacité et d'expertise en fabrication dans le cadre du développement de la technologie WLP.

Portée du marché de l'encapsulation au niveau de la plaquette

Le marché est segmenté en fonction de l'intégration, de la technologie, de l'application et de la technologie de bumping.

- Par intégration

En fonction du niveau d'intégration, le marché du conditionnement au niveau de la plaquette (WLP) se segmente en dispositifs passifs intégrés (IPD), WLP à entrée multiple (Fan-In), WLP à sortie multiple (Fan-Out) et interconnexions traversantes en silicium (TSV). Le segment des IPD a dominé le marché en 2025 grâce à son adoption croissante dans les smartphones, les objets connectés et les applications RF nécessitant des composants miniaturisés et performants. Les IPD offrent des performances électriques supérieures, des capacités parasites réduites et une intégrité du signal améliorée, ce qui les rend essentiels dans les dispositifs de communication haute fréquence. Leur capacité à intégrer de multiples fonctions passives dans un format compact favorise leur adoption massive dans l'électronique grand public et les modules sans fil. Les fabricants privilégient également les IPD car ils permettent une production en grande série à un excellent rapport coût-efficacité. L'intégration croissante de normes de communication avancées telles que la 5G stimule davantage la demande de solutions WLP basées sur les IPD dans les architectures électroniques compactes.

Le segment Fan-Out WLP devrait connaître la croissance la plus rapide entre 2026 et 2033, grâce à son adéquation aux applications exigeant une densité d'E/S élevée et des performances thermiques et électriques améliorées. Le Fan-Out WLP permet une redistribution des connexions, autorisant des intégrations plus complexes tout en conservant une faible épaisseur, ce qui explique sa popularité dans les processeurs mobiles de nouvelle génération et les circuits intégrés de gestion de l'alimentation. Cette technologie est de plus en plus adoptée dans les systèmes avancés d'aide à la conduite (ADAS), l'électronique portable compacte et les modules IoT qui requièrent une dissipation thermique efficace et une fiabilité supérieure. Son évolutivité pour l'intégration hétérogène la positionne avantageusement dans les conceptions de semi-conducteurs en constante évolution. Les développements continus des principaux fabricants de semi-conducteurs pour accroître la capacité Fan-Out alimentent encore davantage sa forte croissance au cours de la période de prévision.

- Par la technologie

En fonction de la technologie utilisée, le marché est segmenté en Flip Chip, WLP conforme, boîtier à l'échelle de la puce conventionnel, boîtier à l'échelle de la puce au niveau de la plaquette (WLCSP), Nano WLP et WLP 3D. Le segment WLCSP a dominé le marché en 2025 grâce à son adoption généralisée dans les appareils mobiles, l'électronique grand public et les capteurs automobiles nécessitant des formats ultra-compacts. Le WLCSP offre des avantages tels qu'une faible inductance, d'excellentes caractéristiques thermiques, une grande fiabilité et un format de puce réel, ce qui en fait une technologie de choix pour la production en grande série. Cette technologie garantit des caractéristiques électriques efficaces, essentielles pour les dispositifs RF, de gestion de l'énergie et MEMS. Le WLCSP réduit également les étapes de traitement et le coût d'encapsulation, favorisant ainsi l'intégration à grande échelle par les principaux fabricants de semi-conducteurs. Sa compatibilité avec les nœuds technologiques avancés assure sa position dominante dans le domaine de l'électronique miniaturisée.

Le segment de l'encapsulation 3D au niveau de la plaquette devrait connaître la croissance la plus rapide d'ici 2033, en raison du besoin croissant d'architectures d'empilement avancées améliorant les performances et la bande passante. Cette technologie favorise l'intégration verticale des puces, permettant des interconnexions plus courtes et des vitesses de traitement plus élevées, un atout crucial pour le calcul haute performance (HPC), les accélérateurs d'intelligence artificielle (IA) et les dispositifs de mémoire de nouvelle génération. L'encapsulation 3D au niveau de la plaquette offre une évolutivité exceptionnelle pour les conceptions de semi-conducteurs complexes exigeant une fonctionnalité accrue dans un format compact. L'adoption croissante de l'intégration 3D dans les centres de données, l'électronique grand public haute performance et l'électronique automobile accélère son déploiement. Les progrès constants des technologies de liaison hybride et de traversée de silicium renforcent le rôle de l'encapsulation 3D au niveau de la plaquette dans l'écosystème de l'encapsulation des semi-conducteurs.

- Sur demande

Selon l'application, le marché du conditionnement au niveau de la plaquette (WLP) est segmenté en électronique, informatique et télécommunications, industrie, automobile, aérospatiale et défense, santé et autres. Le segment électronique a dominé le marché en 2025, porté par la forte consommation de smartphones, d'objets connectés, de tablettes et d'appareils de réalité augmentée/réalité virtuelle (RA/RV) nécessitant des boîtiers de semi-conducteurs compacts et performants. L'adoption croissante de circuits intégrés et de capteurs miniaturisés dans l'électronique grand public renforce encore la demande en WLP. Ce segment bénéficie largement du besoin de puces basse consommation, à dissipation thermique efficace et économiques pour l'électronique portable. Les technologies WLP permettent d'améliorer les fonctionnalités sur une surface réduite, aidant ainsi les fabricants à proposer des appareils plus fins et plus performants. L'innovation continue dans le domaine des appareils grand public à l'échelle mondiale garantit au segment électronique le maintien de sa position de leader.

Le secteur automobile devrait connaître la croissance la plus rapide entre 2026 et 2033, grâce à l'intégration croissante de l'électronique dans les véhicules modernes, notamment les systèmes avancés d'aide à la conduite (ADAS), les systèmes d'infodivertissement, l'électronique de puissance et les plateformes pour véhicules électriques. Les applications automobiles exigent des solutions d'encapsulation robustes et hautement fiables, capables de résister à des températures et des vibrations extrêmes, ce qui fait de la technologie WLP un choix judicieux. L'électrification des véhicules et la mobilité autonome nécessitent des composants semi-conducteurs de pointe offrant une efficacité et des performances de traitement supérieures. La technologie WLP favorise l'intégration compacte des capteurs, microcontrôleurs et circuits intégrés de gestion de l'alimentation, essentiels aux architectures automobiles de nouvelle génération. L'augmentation des investissements des constructeurs automobiles et des équipementiers de rang 1 dans les technologies semi-conductrices avancées contribue également à accélérer la croissance de ce secteur.

- Par Bumping Technology

Selon la technologie de microbilles utilisée, le marché est segmenté en microbilles de cuivre, microbilles de soudure, microbilles d'or et autres. Le segment des microbilles de soudure a dominé le marché en 2025 grâce à sa maturité, sa rentabilité et son utilisation répandue dans divers dispositifs semi-conducteurs. Les microbilles de soudure assurent des connexions électriques et mécaniques fiables pour les puces retournées et les boîtiers au niveau de la plaquette, ce qui les rend idéales pour la production en grande série. Cette méthode offre d'excellentes caractéristiques thermiques et une compatibilité avec diverses applications, notamment les processeurs mobiles, la mémoire et les composants RF. Sa chaîne d'approvisionnement et son infrastructure de production bien établies consolident sa position de leader. Cette technologie demeure un choix privilégié pour optimiser les performances, les coûts et l'efficacité de la production dans le secteur des semi-conducteurs.

Le segment des plots de cuivre devrait enregistrer la croissance la plus rapide au cours de la période de prévision, grâce à sa capacité de transport de courant supérieure, ses performances thermiques améliorées et sa capacité de mise à l'échelle à pas fin. La technologie des plots de cuivre est de plus en plus utilisée dans les dispositifs haute densité et hautes performances, tels que les puces logiques avancées, les processeurs d'IA et les mémoires à large bande passante. Cette technologie permet des interconnexions plus fines et une meilleure résistance à l'électromigration, ce qui la rend adaptée aux architectures de semi-conducteurs compactes modernes. Avec l'essor des méthodes d'encapsulation avancées, telles que l'intégration 2.5D et 3D, la technologie des plots de cuivre devient de plus en plus cruciale. Son adoption croissante dans l'électronique automobile, les centres de données et l'électronique grand public haut de gamme accélère sa croissance jusqu'en 2033.

Analyse régionale du marché de l'encapsulation au niveau de la plaquette

- La région Asie-Pacifique a dominé le marché de l'encapsulation au niveau de la plaquette avec la plus grande part de revenus (52,5 %) en 2025, grâce à la forte présence de pôles de fabrication de semi-conducteurs, à l'adoption croissante de l'encapsulation avancée dans l'électronique grand public et à l'expansion des écosystèmes de fabrication dans les principales économies.

- Les capacités de production compétitives de la région, l'augmentation des investissements dans les technologies au niveau de la plaquette et la croissance rapide de la fabrication de matériel pour appareils mobiles et objets connectés accélèrent l'expansion globale du marché.

- La disponibilité d'ingénieurs qualifiés, les initiatives gouvernementales favorables au développement des semi-conducteurs et la forte consommation de produits électroniques dans les économies émergentes contribuent à l'adoption massive du conditionnement au niveau de la plaquette.

Analyse du marché chinois de l'encapsulation au niveau de la plaquette

En 2025, la Chine détenait la plus grande part du marché de l'encapsulation au niveau de la plaquette en Asie-Pacifique, grâce à sa position dominante dans l'assemblage, le test et la production d'électronique grand public. Le développement de ses capacités de fonderie, le soutien gouvernemental important via des programmes d'autosuffisance dans le secteur des semi-conducteurs et l'intérêt croissant porté aux technologies d'encapsulation avancées sont les principaux moteurs de cette croissance. La demande est également soutenue par la production à grande échelle de smartphones, d'objets connectés et de processeurs hautes performances destinés aux marchés nationaux et internationaux.

Aperçu du marché indien de l'encapsulation au niveau de la plaquette

L'Inde connaît la croissance la plus rapide de la région Asie-Pacifique, alimentée par l'augmentation des investissements dans les installations d'assemblage et de test de semi-conducteurs, la demande croissante d'encapsulation avancée pour les smartphones et l'électronique automobile, et les incitations gouvernementales à la fabrication de semi-conducteurs. L'initiative « Make in India » et l'intérêt croissant des fabricants mondiaux de puces favorisent l'adoption de l'encapsulation au niveau de la plaquette. L'expansion de la production électronique nationale et la forte croissance de la consommation d'appareils grand public contribuent à la dynamique du marché.

Aperçu du marché européen de l'encapsulation au niveau de la plaquette

Le marché européen du conditionnement au niveau de la plaquette est en constante expansion, soutenu par une forte demande de solutions semi-conductrices avancées pour l'électronique automobile, l'automatisation industrielle et les applications à haute fiabilité. La région privilégie une fabrication de haute qualité, des normes réglementaires rigoureuses et les progrès technologiques dans le domaine de la microélectronique haute performance. L'adoption croissante de dispositifs miniaturisés, les investissements continus en R&D et le besoin accru de solutions de conditionnement efficaces pour les capteurs et l'électronique de puissance contribuent également à la croissance du marché.

Analyse du marché allemand de l'encapsulation au niveau de la plaquette

Le marché allemand du conditionnement au niveau de la plaquette est porté par son leadership dans l'électronique automobile, les machines industrielles de pointe et la fabrication de semi-conducteurs de précision. La solide infrastructure de R&D du pays, les collaborations entre les centres de recherche universitaires et les entreprises de semi-conducteurs, ainsi que la demande de composants haute fiabilité pour les applications automobiles et industrielles sont des facteurs clés de cette croissance. L'intégration croissante de capteurs, de dispositifs de puissance et de microcontrôleurs dans les véhicules de nouvelle génération favorise l'adoption de ces solutions de conditionnement avancées.

Analyse du marché britannique de l'encapsulation au niveau de la plaquette

Le marché britannique bénéficie d'un écosystème de conception électronique mature, d'efforts continus pour renforcer la résilience de la chaîne d'approvisionnement des semi-conducteurs et d'investissements croissants dans la recherche avancée en microélectronique et nanofabrication. Une collaboration étroite entre le monde universitaire et l'industrie, la croissance de l'innovation en électronique médicale et l'accent mis sur le développement de semi-conducteurs à haute valeur ajoutée continuent de consolider le rôle du Royaume-Uni dans les technologies d'encapsulation spécialisées. La demande est particulièrement forte dans les domaines de l'instrumentation pour les sciences de la vie, des dispositifs de communication et des systèmes industriels.

Aperçu du marché nord-américain de l'encapsulation au niveau de la plaquette

L'Amérique du Nord devrait connaître la croissance annuelle composée la plus rapide entre 2026 et 2033, portée par la demande croissante de semi-conducteurs haute performance pour l'électronique grand public, les centres de données, l'électronique automobile et les dispositifs d'intelligence artificielle. La région bénéficie de capacités de R&D de pointe, d'une forte présence d'entreprises de semi-conducteurs sans usine de fabrication (fabless) de premier plan et d'une adoption rapide des technologies 3D et d'encapsulation avancée sur plaquettes. La relocalisation croissante de la production de semi-conducteurs et les importants investissements fédéraux dans la fabrication de puces contribuent également à l'expansion du marché.

Aperçu du marché américain de l'encapsulation au niveau de la plaquette

En 2025, les États-Unis détenaient la plus grande part du marché nord-américain du conditionnement au niveau de la plaquette, grâce à un écosystème d'innovation performant dans le domaine des semi-conducteurs, des programmes de R&D avancés en matière de conditionnement et une importante capacité de production pour le calcul haute performance, les dispositifs de communication et l'électronique automobile. L'accent mis par le pays sur le leadership technologique, ses investissements conséquents dans la conception de puces et la présence de grands fabricants et fonderies de semi-conducteurs contribuent à une forte demande en conditionnement au niveau de la plaquette. L'intégration croissante de l'IA, du cloud computing et de l'électronique pour véhicules électriques renforce encore la position des États-Unis sur le marché régional.

Part de marché du conditionnement au niveau de la plaquette

L'industrie du packaging au niveau de la plaquette est principalement dominée par des entreprises bien établies, notamment :

- JCET Group Co., Ltd. (Chine)

- NEMOTEK Technologie (Maroc)

- Chipbond Technology Corporation (Taïwan)

- Fujitsu (Japon)

- Powertech Technology Inc. (Taïwan)

- China Wafer Level CSP Co., Ltd. (Chine)

- Siliconware Precision Industries Co., Ltd. (Taïwan)

- Amkor Technology (États-Unis)

- IQE PLC (Royaume-Uni)

- ChipMOS Technologies Inc. (Taïwan)

- Deca Technologies (États-Unis)

- Qualcomm Technologies, Inc. (États-Unis)

- Toshiba Corporation (Japon)

- Tokyo Electron Limited (Japon)

- Applied Materials, Inc. (États-Unis)

- Lam Research Corporation (États-Unis)

- ASML (Pays-Bas)

- Infineon Technologies AG (Allemagne)

- KLA Corporation (États-Unis)

- Marvell (États-Unis)

Dernières évolutions du marché mondial de l'encapsulation au niveau de la plaquette

- En septembre 2024, Samsung Electronics a annoncé un développement majeur de son écosystème d'encapsulation avancée, intégrant des capacités améliorées d'encapsulation au niveau de la plaquette et d'assemblage de chiplets dans ses usines de Corée du Sud. Cette initiative renforce sa position dans l'intégration hétérogène, soutient la demande croissante d'encapsulation de semi-conducteurs haute densité pour les applications d'IA et de calcul haute performance (HPC), et accélère l'adoption des technologies WLP de nouvelle génération en améliorant l'efficacité de la production et en réduisant les cycles de développement.

- En août 2024, ASE Technology Holding a annoncé son intention de moderniser ses usines taïwanaises avec des plateformes de test au niveau de la plaquette de nouvelle génération et des systèmes d'automatisation avancés. Cet investissement renforce la stabilité de la production, permet de fabriquer des volumes plus importants de solutions WLP compactes et fiables, et consolide la capacité de l'entreprise à répondre à la demande croissante des secteurs de l'électronique automobile, de l'Internet des objets (IoT) et des applications grand public de pointe.

- En mars 2024, l'Université d'État de l'Arizona et Deca Technologies se sont associées pour créer le premier centre de recherche et développement nord-américain dédié à l'encapsulation au niveau de la plaquette par diffusion (FOWLP). Cette collaboration renforce le leadership technologique américain dans le domaine de l'encapsulation avancée, accélère l'innovation dans les architectures FOWLP et soutient la résilience de la chaîne d'approvisionnement nationale des semi-conducteurs en favorisant le développement conjoint, par l'industrie et le monde universitaire, des procédés de nouvelle génération.

- En mars 2024, Taiwan Semiconductor Manufacturing Company Limited a annoncé son intention d'accroître ses capacités de production de puces à conditionnement avancé au Japon, dans le cadre de sa stratégie de développement international. Cette expansion renforce les capacités de production régionales, diversifie la chaîne d'approvisionnement et répond à la demande croissante de technologies de conditionnement au niveau de la plaquette utilisées dans les dispositifs hautes performances et les applications logiques avancées.

- En juin 2023, Onto Innovation a inauguré son Centre d'excellence en applications pour l'encapsulation au niveau des panneaux à son siège social de Wilmington, dans le Massachusetts. Ce centre offre aux clients un accès direct aux équipements, aux logiciels et aux environnements de processus collaboratifs qui accélèrent les feuilles de route technologiques, optimisent les processus PLP et WLP et réduisent le délai de mise sur le marché des solutions d'encapsulation de semi-conducteurs avancées.

SKU-

Accédez en ligne au rapport sur le premier cloud mondial de veille économique

- Tableau de bord d'analyse de données interactif

- Tableau de bord d'analyse d'entreprise pour les opportunités à fort potentiel de croissance

- Accès d'analyste de recherche pour la personnalisation et les requêtes

- Analyse de la concurrence avec tableau de bord interactif

- Dernières actualités, mises à jour et analyse des tendances

- Exploitez la puissance de l'analyse comparative pour un suivi complet de la concurrence

Méthodologie de recherche

La collecte de données et l'analyse de l'année de base sont effectuées à l'aide de modules de collecte de données avec des échantillons de grande taille. L'étape consiste à obtenir des informations sur le marché ou des données connexes via diverses sources et stratégies. Elle comprend l'examen et la planification à l'avance de toutes les données acquises dans le passé. Elle englobe également l'examen des incohérences d'informations observées dans différentes sources d'informations. Les données de marché sont analysées et estimées à l'aide de modèles statistiques et cohérents de marché. De plus, l'analyse des parts de marché et l'analyse des tendances clés sont les principaux facteurs de succès du rapport de marché. Pour en savoir plus, veuillez demander un appel d'analyste ou déposer votre demande.

La méthodologie de recherche clé utilisée par l'équipe de recherche DBMR est la triangulation des données qui implique l'exploration de données, l'analyse de l'impact des variables de données sur le marché et la validation primaire (expert du secteur). Les modèles de données incluent la grille de positionnement des fournisseurs, l'analyse de la chronologie du marché, l'aperçu et le guide du marché, la grille de positionnement des entreprises, l'analyse des brevets, l'analyse des prix, l'analyse des parts de marché des entreprises, les normes de mesure, l'analyse globale par rapport à l'analyse régionale et des parts des fournisseurs. Pour en savoir plus sur la méthodologie de recherche, envoyez une demande pour parler à nos experts du secteur.

Personnalisation disponible

Data Bridge Market Research est un leader de la recherche formative avancée. Nous sommes fiers de fournir à nos clients existants et nouveaux des données et des analyses qui correspondent à leurs objectifs. Le rapport peut être personnalisé pour inclure une analyse des tendances des prix des marques cibles, une compréhension du marché pour d'autres pays (demandez la liste des pays), des données sur les résultats des essais cliniques, une revue de la littérature, une analyse du marché des produits remis à neuf et de la base de produits. L'analyse du marché des concurrents cibles peut être analysée à partir d'une analyse basée sur la technologie jusqu'à des stratégies de portefeuille de marché. Nous pouvons ajouter autant de concurrents que vous le souhaitez, dans le format et le style de données que vous recherchez. Notre équipe d'analystes peut également vous fournir des données sous forme de fichiers Excel bruts, de tableaux croisés dynamiques (Fact book) ou peut vous aider à créer des présentations à partir des ensembles de données disponibles dans le rapport.