Global Wafer Level Packaging Market

시장 규모 (USD 10억)

연평균 성장률 :

%

USD

10.43 Billion

USD

47.92 Billion

2025

2033

USD

10.43 Billion

USD

47.92 Billion

2025

2033

| 2026 –2033 | |

| USD 10.43 Billion | |

| USD 47.92 Billion | |

|

|

|

|

글로벌 웨이퍼 레벨 패키징 시장 세분화, 통합(통합 수동 소자, 팬 인 WLP, 팬 아웃 WLP 및 실리콘 관통 비아), 기술(플립 칩, 호환 WLP, 기존 칩 스케일 패키지, 웨이퍼 레벨 칩 스케일 패키지, 나노 웨이퍼 레벨 패키징 및 3D 웨이퍼 레벨 패키징), 응용 분야(전자, IT 및 통신, 산업, 자동차, 항공우주 및 방위, 의료 및 기타), 범핑 기술(구리 필러, 솔더 범핑, 금 범핑 및 기타) - 산업 동향 및 2033년까지의 예측

웨이퍼 레벨 패키징 시장 규모

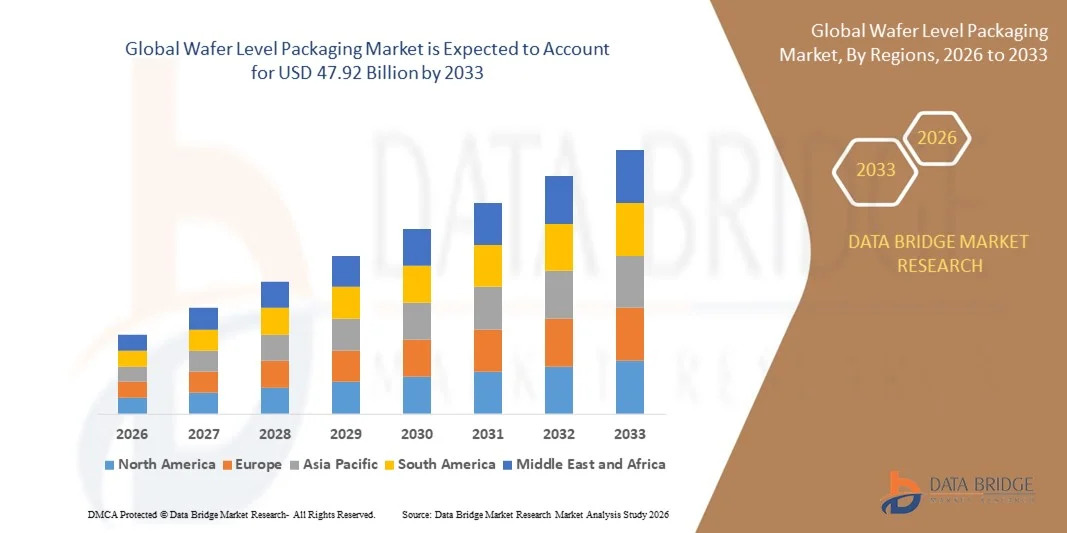

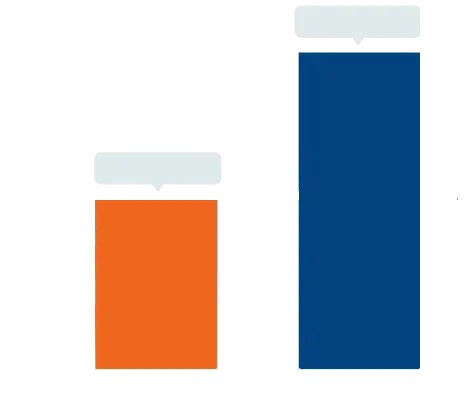

- 글로벌 웨이퍼 레벨 패키징 시장 규모는 2025년에 104억 3천만 달러 로 평가되었으며 예측 기간 동안 21.0%의 CAGR 로 2033년까지 479억 2천만 달러 에 도달할 것으로 예상됩니다 .

- 시장 성장은 주로 가전제품, 자동차 및 산업용 애플리케이션 전반에 걸쳐 소형, 고성능, 에너지 효율적인 반도체 장치에 대한 수요 증가에 의해 촉진되며, 제조업체는 기능을 향상하고 폼 팩터를 줄이기 위해 고급 웨이퍼 수준 패키징 방법을 채택하도록 장려합니다.

- 또한 스마트폰, 웨어러블, IoT 기기의 생산량 증가로 인해 향상된 열 성능, 더 높은 입출력 밀도, 뛰어난 전기적 특성에 대한 필요성이 높아지고 있어 웨이퍼 레벨 패키징은 차세대 전자 시스템에 필수적인 기술이 되었습니다.

웨이퍼 레벨 패키징 시장 분석

- 웨이퍼 단계에서 여러 기능을 통합할 수 있는 웨이퍼 레벨 패키징은 광범위한 최종 사용 장치에 대해 더 높은 소형화, 향상된 신뢰성 및 향상된 전기적 성능을 제공할 수 있는 능력으로 인해 현대 반도체 제조에 중요한 기술이 되고 있습니다.

- 웨이퍼 레벨 패키징에 대한 수요 증가는 주로 모바일 통신, 센서 기술, AI 기반 전자 기술의 급속한 발전과 소비자, 자동차 및 산업 분야에서 필요한 더 작고 빠르고 효율적인 반도체 구성 요소에 대한 글로벌 전환에 의해 주도됩니다.

- 아시아 태평양 지역은 반도체 제조 허브의 강력한 존재감, 가전제품의 고급 패키징 채택 증가, 주요 경제권 전반의 제조 생태계 확대로 인해 2025년 웨이퍼 레벨 패키징 시장 점유율 52.5%를 차지하며 시장을 장악했습니다.

- 북미는 가전제품, 데이터 센터, 자동차 전자제품 및 AI 기반 기기에서 고성능 반도체에 대한 수요가 증가함에 따라 예측 기간 동안 웨이퍼 레벨 패키징 시장에서 가장 빠르게 성장하는 지역이 될 것으로 예상됩니다.

- 집적 수동 소자(IPD) 부문은 소형화, 고성능 부품을 필요로 하는 스마트폰, 웨어러블 기기, 그리고 RF 애플리케이션에서의 채택 증가로 2025년 시장 점유율을 차지하며 시장을 장악했습니다. IPD는 탁월한 전기적 성능, 기생 성분 감소, 그리고 향상된 신호 무결성을 제공하여 고주파 통신 기기에 필수적인 요소입니다. 여러 수동 기능을 소형 풋프린트에 통합할 수 있는 능력은 가전제품과 무선 모듈 전반에 걸쳐 높은 채택률을 보이고 있습니다. 제조업체들은 또한 IPD가 우수한 비용 효율성과 함께 대량 생산을 지원하기 때문에 IPD를 선호합니다. 5G와 같은 첨단 통신 표준의 통합 증가는 소형 전자 아키텍처에서 IPD 기반 WLP 솔루션에 대한 수요를 더욱 증가시키고 있습니다.

보고서 범위 및 웨이퍼 레벨 패키징 시장 세분화

|

속성 |

웨이퍼 레벨 패키징 주요 시장 통찰력 |

|

다루는 세그먼트 |

|

|

포함 국가 |

북아메리카

유럽

아시아 태평양

중동 및 아프리카

남아메리카

|

|

주요 시장 참여자 |

|

|

시장 기회 |

|

|

부가가치 데이터 정보 세트 |

Data Bridge Market Research에서 큐레이팅한 시장 보고서에는 시장 가치, 성장률, 세분화, 지리적 범위, 주요 업체 등 시장 시나리오에 대한 통찰력 외에도 수입 수출 분석, 생산 능력 개요, 생산 소비 분석, 가격 추세 분석, 기후 변화 시나리오, 공급망 분석, 가치 사슬 분석, 원자재/소모품 개요, 공급업체 선택 기준, PESTLE 분석, Porter 분석 및 규제 프레임워크가 포함됩니다. |

웨이퍼 레벨 패키징 시장 동향

고급 팬아웃 및 3D 웨이퍼 레벨 패키징 기술의 채택 증가

- 제조업체들이 차세대 반도체 소자의 성능 향상과 집적도 향상을 우선시함에 따라 웨이퍼 레벨 패키징 시장은 첨단 팬아웃 및 3D 아키텍처로의 급격한 전환을 경험하고 있습니다. 이러한 추세는 스마트폰, 고성능 컴퓨팅, 자동차 전장 등 다양한 분야에서 향상된 전기적 성능, 더 얇은 폼팩터, 그리고 향상된 열 효율에 대한 요구가 증가함에 따라 형성되고 있습니다.

- 예를 들어, Deca Technologies는 복잡한 칩 아키텍처에 대한 더 높은 처리량과 향상된 설계 유연성을 추구하는 선도적인 반도체 제조업체를 지원하기 위해 팬아웃 패키징 기능을 확장하여 업계 참여자가 확장 가능한 팬아웃 플랫폼을 통해 혁신을 가속화하는 방식을 보여주었습니다.

- 팬아웃 및 3D 웨이퍼 레벨 패키징은 더 짧은 인터커넥트, 더 높은 I/O 밀도, 그리고 향상된 시스템 인 패키지(SIP) 집적도를 가능하게 하여, 강력한 전력 효율과 컴팩트한 설계를 요구하는 첨단 프로세서, AI 가속기, 엣지 컴퓨팅 장치에 필수적입니다. 이러한 변화는 비용 절감과 성능 향상을 위한 제조 최적화 강화를 통해 더욱 가속화됩니다.

- 이종 집적화에 대한 수요는 칩 제조업체들이 메모리, 로직, RF 부품 등 여러 기능을 소형 패키지에 통합함에 따라 이러한 첨단 WLP 방식의 도입을 뒷받침하고 있습니다. 이러한 추세는 기존 2D 아키텍처의 스케일링 한계를 지원해야 할 필요성에서도 기인합니다.

- 기업들은 차세대 패키징 기술을 위한 생산 역량 확대 및 R&D 강화에 집중하고 있으며, 이를 통해 다양한 마이크로전자 응용 분야에서 팬아웃 및 3D 구조 도입이 가속화되고 있습니다. 이러한 집중은 반도체 패키징의 성능 및 소형화에 대한 기대치를 변화시키고 있습니다.

- 더 작은 공간에서 더 높은 시스템 기능을 달성하려는 강조가 커지면서 제조업체는 고급 웨이퍼 수준 패키징을 향해 나아가고 있으며, 이는 가전제품, 자동차 및 고성능 컴퓨팅 시장에서 지속적인 채택을 위한 강력한 추진력으로 이어지고 있습니다.

웨이퍼 레벨 패키징 시장 동향

운전사

소형화 및 고성능 반도체 소자에 대한 수요 증가

- 소형, 전력 효율, 고성능 반도체 소자에 대한 소비자 및 산업계의 수요 증가로 인해 다양한 애플리케이션에 걸쳐 웨이퍼 레벨 패키징 솔루션 도입이 활발해지고 있습니다. 전자 기기가 더욱 소형화되고 첨단화됨에 따라, WLP는 최신 칩 아키텍처에 필요한 밀도, 속도, 신뢰성을 제공합니다.

- 예를 들어, Amkor Technology는 더 얇은 프로필과 더 높은 기능적 성능을 요구하는 스마트폰 제조업체와 컴퓨팅 장치 제조업체의 증가하는 요구를 충족하기 위해 고급 웨이퍼 레벨 패키징 포트폴리오를 계속 확장하고 있습니다.

- 웨어러블, IoT 노드, 스마트폰 등 가전제품의 소형화 추세는 높은 I/O 밀도, 향상된 신호 무결성, 그리고 지연 시간 단축을 제공하는 패키징 솔루션에 대한 수요를 촉진하고 있습니다. WLP는 상호 연결 길이를 최소화하고 칩 패키지 내 전기 경로를 최적화함으로써 이러한 기능을 구현합니다.

- 저전력 소비와 향상된 디바이스 기능에 대한 기대가 커짐에 따라 제조업체들은 소비자 및 산업용 애플리케이션 모두에서 웨이퍼 레벨 패키징을 선호하는 통합 솔루션으로 채택하고 있습니다. 이는 차세대 반도체 개발에서 웨이퍼 레벨 패키징의 중요한 역할을 더욱 강화합니다.

- 고성능 컴퓨팅 및 소형 전자 제품에 대한 수요 급증으로 WLP는 필수 기술로 자리매김하고 있으며, 칩 소형화 및 성능 향상을 가능하게 하는 데 있어 WLP의 중요성이 더욱 커지고 있습니다.

제지/도전

높은 자본 투자 및 복잡한 제조 요구 사항

- 웨이퍼 레벨 패키징 시장은 첨단 제조 인프라에 필요한 높은 자본 투자와 관련 생산 공정의 복잡성으로 인해 심각한 어려움에 직면해 있습니다. WLP 제조 라인을 구축하려면 고가의 장비, 정밀 공구, 그리고 특수 클린룸 환경이 필요하며, 이는 신규 진입 기업과 소규모 업체에게 장벽이 됩니다.

- 예를 들어, 최첨단 리소그래피, 본딩, 계측 장비에 투자하는 기업들은 상당한 재정적 부담에 직면하여 생산 능력을 빠르게 확장하는 데 제약을 받을 수 있습니다. 팬아웃, 3D 스태킹, 이종 집적화와 같은 첨단 WLP 공정은 정교한 제조 전문성, 정밀한 정렬, 그리고 첨단 재료 처리 기술을 요구하며, 이는 운영 복잡성을 증가시킵니다. 이러한 요구 사항으로 인해 많은 반도체 패키징 시설에서 공정 최적화는 주요 과제로 대두되고 있습니다.

- R&D, 공정 자동화, 품질 보증에 대한 지속적인 투자 필요성은 비용 압박을 더욱 가중시키고 있으며, 특히 패키징 기술이 더 높은 집적도와 더 미세한 피처 크기를 지원하도록 발전함에 따라 더욱 그렇습니다. 이러한 복잡성으로 인해 비용에 민감한 제조업체의 도입이 지연되고 있습니다.

- 생산 기술이 발전함에 따라, 여러 제조 단계와 결함 위험 증가로 인해 수율 안정성과 공정 균일성 유지가 점점 더 어려워지고 있으며, 이는 운영상의 어려움으로 이어지고 있습니다. 이러한 문제는 확장성과 비용 효율성에 영향을 미칩니다.

- 높은 자본 지출 요구 사항과 복잡한 제조 워크플로의 조합은 더 폭넓은 채택을 위한 지속적인 과제를 제시하며, 이 섹션은 WLP 확장에서 비용, 역량 및 제조 전문성 제약을 해결하는 것의 중요성에 대한 결론으로 마무리됩니다.

웨이퍼 레벨 패키징 시장 범위

시장은 통합, 기술, 응용 프로그램, 범핑 기술을 기준으로 세분화됩니다.

- 통합을 통해

웨이퍼 레벨 패키징 시장은 집적도를 기준으로 집적 수동 소자(IPD), 팬인 WLP, 팬아웃 WLP, 그리고 TSV(Through-Silicon Via)로 구분됩니다. 집적 수동 소자 부문은 소형 고성능 부품을 필요로 하는 스마트폰, 웨어러블 기기, 그리고 RF 애플리케이션에서의 채택 증가로 2025년 시장을 장악했습니다. IPD는 탁월한 전기적 성능, 기생 성분 감소, 그리고 향상된 신호 무결성을 제공하여 고주파 통신 기기에 필수적인 요소입니다. 여러 수동 기능을 소형 풋프린트에 통합할 수 있는 능력은 가전제품과 무선 모듈 전반에 걸쳐 높은 채택률을 보이고 있습니다. 제조업체들은 또한 IPD가 대량 생산과 뛰어난 비용 효율성을 지원하기 때문에 선호합니다. 5G와 같은 첨단 통신 표준의 통합 증가는 소형 전자 아키텍처에서 IPD 기반 WLP 솔루션에 대한 수요를 더욱 증가시키고 있습니다.

팬아웃 WLP(Fan-Out WLP) 부문은 높은 I/O 밀도와 향상된 열 및 전기적 성능이 요구되는 애플리케이션에 대한 적합성으로 인해 2026년부터 2033년까지 가장 빠른 성장을 보일 것으로 예상됩니다. 팬아웃 WLP는 연결 재분배를 지원하여 얇은 두께를 유지하면서도 더욱 복잡한 패키징을 가능하게 하여 차세대 모바일 프로세서 및 전력 관리 IC에서 널리 사용됩니다. 이 기술은 효율적인 방열과 뛰어난 신뢰성을 요구하는 첨단 운전자 보조 시스템(ADAS), 소형 웨어러블 전자 제품, IoT 모듈에 점점 더 많이 채택되고 있습니다. 이 기술은 이기종 통합을 위한 확장성이 뛰어나 끊임없이 진화하는 반도체 설계에 강력한 입지를 확보하고 있습니다. 주요 반도체 기업들이 팬아웃 용량을 확장하기 위해 지속적으로 개발하고 있어 예측 기간 동안 팬아웃 WLP의 높은 성장 궤도가 더욱 가속화될 것입니다.

- 기술로

기술 기반으로 시장은 플립칩, 컴플라이언트 WLP, 기존 칩 스케일 패키지, 웨이퍼 레벨 칩 스케일 패키지(WLCSP), 나노 WLP, 3D WLP로 구분됩니다. WLCSP는 초소형 폼팩터를 요구하는 모바일, 가전제품, 자동차 센서 분야에서 널리 채택되면서 2025년 시장을 장악했습니다. WLCSP는 낮은 인덕턴스, 우수한 열 특성, 높은 신뢰성, 그리고 칩 사이즈에 맞는 패키징 등의 이점을 제공하여 대량 생산에 매우 선호됩니다. 이 기술은 RF, 전력 관리, MEMS 장치에 필수적인 효율적인 전기적 특성을 지원합니다. 또한, WLCSP는 공정 단계와 패키징 비용을 줄여 주요 반도체 제조업체의 대규모 집적화를 촉진합니다. 고급 노드와의 호환성은 소형 전자 제품 분야에서 지속적인 우위를 보장합니다.

3D 웨이퍼 레벨 패키징 부문은 성능과 대역폭을 향상시키는 첨단 스태킹 아키텍처에 대한 수요 증가로 2033년까지 가장 빠른 성장을 기록할 것으로 예상됩니다. 이 기술은 다이의 수직적 통합을 지원하여 상호 연결 간격을 줄이고 처리 속도를 향상시키며, 이는 HPC, AI 가속기, 차세대 메모리 소자에 필수적입니다. 3D WLP는 소형 크기 내에서 더 높은 기능을 요구하는 복잡한 반도체 설계에 탁월한 확장성을 제공합니다. 데이터 센터, 고성능 가전제품, 자동차 전장 분야에서 3D 집적 기술의 도입이 증가함에 따라 3D WLP의 도입이 가속화되고 있습니다. 실리콘 관통전극(TSV) 및 하이브리드 본딩 기술의 지속적인 발전은 반도체 패키징 생태계에서 3D WLP의 역할을 강화하고 있습니다.

- 응용 프로그램별

웨이퍼 레벨 패키징 시장은 응용 분야별로 전자, IT 및 통신, 산업, 자동차, 항공우주 및 방위, 의료, 기타로 구분됩니다. 전자 부문은 2025년 시장을 장악했으며, 이는 소형 고성능 반도체 패키지를 필요로 하는 스마트폰, 웨어러블, 태블릿, AR/VR 기기의 폭발적인 수요 증가에 힘입은 것입니다. 가전제품에 소형 집적 회로 및 센서가 점점 더 많이 도입됨에 따라 WLP 수요가 더욱 증가할 것으로 예상됩니다. 이 부문은 휴대용 전자제품에 저전력, 열 효율, 비용 효율적인 칩이 요구됨에 따라 상당한 수혜를 입고 있습니다. WLP 기술은 제한된 보드 공간에서 향상된 기능을 제공하여 제조업체가 더욱 세련되고 고성능 기기를 제공할 수 있도록 지원합니다. 전 세계적으로 가전제품의 지속적인 혁신을 통해 전자 부문은 선도적인 입지를 유지하고 있습니다.

자동차 부문은 ADAS, 인포테인먼트 시스템, 전력 전자 장치, 전기차 플랫폼 등 최신 차량의 전자 부품 증가로 인해 2026년부터 2033년까지 가장 빠른 성장을 보일 것으로 예상됩니다. 자동차 애플리케이션은 극한의 온도와 진동을 견딜 수 있는 고신뢰성, 견고한 패키징 솔루션을 요구하기 때문에 WLP(웨이퍼 레벨 패키징)는 매력적인 선택입니다. 차량 전기화 및 자율주행으로의 전환은 탁월한 효율과 처리 성능을 제공하는 첨단 반도체 부품을 필요로 합니다. WLP는 차세대 자동차 아키텍처에 필수적인 센서, 마이크로컨트롤러, 전력 관리 IC의 소형 집적을 지원합니다. 자동차 OEM과 1차 공급업체의 첨단 반도체 기술 투자 증가는 이 부문의 성장을 더욱 가속화하고 있습니다.

- 범핑 기술로

범핑 기술을 기준으로 시장은 구리 필러, 솔더 범핑, 금 범핑, 기타로 구분됩니다. 솔더 범핑 부문은 성숙도, 비용 효율성, 그리고 다양한 반도체 소자에 널리 사용됨에 따라 2025년 시장을 장악했습니다. 솔더 범핑은 플립칩 및 웨이퍼 레벨 패키징에 안정적인 전기적, 기계적 연결을 제공하여 대량 생산에 이상적입니다. 이 기술은 강력한 열적 특성과 모바일 프로세서, 메모리, RF 부품을 포함한 다양한 애플리케이션과의 호환성을 지원합니다. 오랜 기간 구축된 공급망과 제조 인프라는 솔더 범핑의 선도적 입지를 더욱 공고히 합니다. 이 기술은 주류 반도체 생산에서 성능, 비용, 그리고 제조 효율성의 균형을 맞추는 데 있어 여전히 선호되는 기술입니다.

구리 필러(Copper Pillar) 부문은 뛰어난 전류 전달 능력, 향상된 열 성능, 그리고 미세 피치 확장성으로 인해 예측 기간 동안 가장 빠른 성장을 기록할 것으로 예상됩니다. 구리 필러 범핑은 첨단 로직 칩, AI 프로세서, 고대역폭 메모리와 같은 고밀도 및 고성능 장치에 점점 더 많이 사용되고 있습니다. 이 기술은 더 얇은 상호 연결과 더 나은 일렉트로마이그레이션 저항을 지원하여 최신 소형 반도체 아키텍처에 적합합니다. 2.5D 및 3D 집적화와 같은 첨단 패키징 방식이 확대됨에 따라 구리 필러 범핑의 중요성이 더욱 커지고 있습니다. 자동차 전장, 데이터 센터, 그리고 프리미엄 가전제품 분야에서의 채택 증가는 2033년까지 구리 필러 범핑의 성장 모멘텀을 가속화할 것입니다.

웨이퍼 레벨 패키징 시장 지역 분석

- 아시아 태평양 지역은 2025년 52.5%의 가장 큰 매출 점유율로 웨이퍼 레벨 패키징 시장을 장악했으며, 이는 반도체 제조 허브의 강력한 존재감, 가전제품에서 고급 패키징 채택 증가, 주요 경제권 전반의 제조 생태계 확대에 힘입은 것입니다.

- 이 지역의 비용 효율적인 생산 능력, 웨이퍼 수준 기술에 대한 투자 증가, 모바일 장치 및 IoT 하드웨어 제조의 급속한 성장은 전반적인 시장 확장을 가속화하고 있습니다.

- 숙련된 엔지니어링 인재의 가용성, 반도체 개발을 위한 정부 지원 이니셔티브, 신흥 경제권에서의 대규모 전자 소비는 웨이퍼 레벨 패키징의 실질적인 채택에 기여하고 있습니다.

중국 웨이퍼 레벨 패키징 시장 통찰력

중국은 반도체 조립, 테스트, 가전제품 생산 분야에서의 지배적인 입지를 바탕으로 2025년 아시아 태평양 웨이퍼 레벨 패키징 시장에서 최대 점유율을 차지할 것으로 예상됩니다. 중국의 파운드리 역량 확대, 반도체 자립 프로그램을 통한 강력한 정부 지원, 그리고 첨단 패키징 기술에 대한 집중 강화는 중국 성장의 핵심 동력입니다. 스마트폰, 웨어러블 기기, 고성능 프로세서의 국내 및 글로벌 시장 대량 생산 또한 수요 증가를 뒷받침하고 있습니다.

인도 웨이퍼 레벨 패키징 시장 통찰력

인도는 반도체 조립 및 테스트 시설 투자 증가, 스마트폰 및 자동차 전장 부품의 첨단 패키징 수요 증가, 그리고 정부 주도의 반도체 제조 인센티브 정책에 힘입어 아시아 태평양 지역에서 가장 빠른 성장을 기록하고 있습니다. "메이크 인 인디아(Make in India)" 정책과 글로벌 칩 제조업체들의 관심 증가는 웨이퍼 레벨 패키징(WLP) 도입을 강화하고 있습니다. 국내 전자 제품 제조 확대와 소비자 기기 소비의 빠른 성장은 강력한 시장 모멘텀을 뒷받침하고 있습니다.

유럽 웨이퍼 레벨 패키징 시장 통찰력

유럽 웨이퍼 레벨 패키징 시장은 자동차 전장, 산업 자동화, 고신뢰성 애플리케이션 분야의 첨단 반도체 솔루션에 대한 강력한 수요에 힘입어 꾸준히 성장하고 있습니다. 이 지역은 고품질 제조, 엄격한 규제 기준, 그리고 고성능 마이크로일렉트로닉스 분야의 기술 발전을 강조합니다. 소형화 장치 채택 증가, 지속적인 R&D 투자, 그리고 센서 및 전력 전자 장치의 효율적인 패키징에 대한 수요 증가는 시장 성장을 더욱 가속화하고 있습니다.

독일 웨이퍼 레벨 패키징 시장 통찰력

독일의 웨이퍼 레벨 패키징 시장은 자동차 전자 장치, 첨단 산업 기계, 정밀 반도체 제조 분야의 선도적 입지를 바탕으로 성장하고 있습니다. 독일의 탄탄한 R&D 인프라, 학계와 반도체 기업 간의 협력, 그리고 자동차 및 산업 분야에서 고신뢰성 부품에 대한 수요가 이러한 성장의 핵심 요인입니다. 차세대 차량에서 센서, 전력 소자, 마이크로컨트롤러의 집적도가 증가함에 따라 첨단 패키징 도입이 확대되고 있습니다.

영국 웨이퍼 레벨 패키징 시장 통찰력

영국 시장은 성숙한 전자 설계 생태계, 반도체 공급망 회복력 강화를 위한 지속적인 노력, 그리고 마이크로일렉트로닉스 및 나노 제조 분야 첨단 연구 투자 증가에 힘입어 성장하고 있습니다. 탄탄한 산학 협력, 의료용 전자 기술 혁신의 성장, 그리고 고부가가치 반도체 개발에 대한 집중은 특수 패키징 기술 분야에서 영국의 입지를 더욱 강화하고 있습니다. 특히 생명 과학 계측기, 통신 기기, 산업 시스템 분야의 수요가 강세를 보이고 있습니다.

북미 웨이퍼 레벨 패키징 시장 통찰력

북미 지역은 가전제품, 데이터센터, 자동차 전장, AI 기반 기기 등 고성능 반도체 수요 증가에 힘입어 2026년부터 2033년까지 가장 빠른 연평균 성장률(CAGR)을 기록할 것으로 예상됩니다. 최첨단 R&D 역량, 선도적인 팹리스 반도체 기업들의 강력한 입지, 그리고 3D 및 첨단 웨이퍼 패키징 기술의 빠른 도입은 북미 지역의 강점입니다. 반도체 제조의 리쇼어링(reshoring) 증가와 칩 제조에 대한 연방 정부의 대규모 투자 또한 시장 확대를 가속화하고 있습니다.

미국 웨이퍼 레벨 패키징 시장 통찰력

미국은 강력한 반도체 혁신 생태계, 첨단 패키징 R&D 프로그램, 그리고 고성능 컴퓨팅, 통신 장치, 자동차 전장 분야의 상당한 제조 역량을 바탕으로 2025년 북미 웨이퍼 레벨 패키징 시장에서 가장 큰 점유율을 차지할 것으로 예상됩니다. 미국은 기술 리더십 강화, 칩 설계에 대한 적극적인 투자, 그리고 주요 반도체 제조업체와 파운드리의 입지를 바탕으로 웨이퍼 레벨 패키징에 대한 수요를 꾸준히 확대하고 있습니다. AI, 클라우드 컴퓨팅, 그리고 EV 전자 기술의 통합 확대는 미국이 이 지역 시장에서 차지하는 입지를 더욱 강화할 것입니다.

웨이퍼 레벨 패키징 시장 점유율

웨이퍼 레벨 패키징 산업은 주로 다음을 포함한 잘 확립된 회사들이 주도하고 있습니다.

- JCET 그룹 유한회사(중국)

- NEMOTEK Technologie(모로코)

- 칩본드 테크놀로지 코퍼레이션(대만)

- 후지쯔(일본)

- 파워텍 테크놀로지 주식회사(대만)

- 중국 웨이퍼 레벨 CSP 유한회사(중국)

- 실리콘웨어 정밀산업 주식회사(대만)

- 앰코 테크놀로지(미국)

- IQE PLC(영국)

- ChipMOS Technologies Inc.(대만)

- 데카 테크놀로지스(미국)

- Qualcomm Technologies, Inc.(미국)

- 도시바 주식회사(일본)

- 도쿄 일렉트론 주식회사(일본)

- Applied Materials, Inc.(미국)

- 램리서치코퍼레이션(미국)

- ASML(네덜란드)

- Infineon Technologies AG(독일)

- KLA Corporation(미국)

- 마벨(미국)

글로벌 웨이퍼 레벨 패키징 시장의 최신 동향

- 2024년 9월, 삼성전자는 향상된 웨이퍼 레벨 패키징 및 칩렛 어셈블리 역량을 국내 생산 시설에 통합하여 첨단 패키징 생태계를 대대적으로 확장한다고 발표했습니다. 이 이니셔티브는 이종 집적화 분야에서 삼성전자의 입지를 강화하고, AI 및 HPC 애플리케이션에서 고밀도 반도체 패키징 수요 증가를 지원하며, 생산 효율을 개선하고 개발 주기를 단축함으로써 차세대 WLP 기술 도입을 가속화합니다.

- 2024년 8월, ASE Technology Holding은 대만 생산 시설을 차세대 웨이퍼 레벨 테스트 플랫폼과 첨단 자동화 시스템으로 업그레이드할 계획을 발표했습니다. 이 투자는 생산 안정성을 높이고, 소형의 안정적인 WLP 솔루션 생산량을 늘리며, 자동차 전자 장치, IoT 기기 및 첨단 소비자 애플리케이션의 증가하는 수요를 충족할 수 있는 회사의 역량을 강화합니다.

- 2024년 3월, 애리조나 주립대학교와 데카 테크놀로지스는 북미 최초의 팬아웃 웨이퍼 레벨 패키징 전담 연구 개발 센터를 설립하기 위해 파트너십을 체결했습니다. 이 협력은 첨단 패키징 분야에서 미국의 기술 리더십을 강화하고, FOWLP 아키텍처 혁신을 가속화하며, 차세대 공정에 대한 산학 협력 개발을 촉진하여 국내 반도체 공급망의 회복탄력성을 지원합니다.

- 2024년 3월, 대만 반도체 제조회사(TSMC)는 광범위한 글로벌 확장 전략의 일환으로 일본 내 첨단 칩 패키징 생산 능력 확대 계획을 발표했습니다. 이번 확장은 지역 제조 역량을 향상시키고, 공급망 다각화를 강화하며, 고성능 디바이스 및 첨단 로직 애플리케이션에 사용되는 웨이퍼 레벨 패키징 기술에 대한 수요 증가를 뒷받침합니다.

- 2023년 6월, Onto Innovation은 매사추세츠주 윌밍턴 본사에 패널 레벨 패키징을 위한 애플리케이션 센터 오브 엑설런스(Applications Center of Excellence)를 설립했습니다. 이 시설은 고객에게 기술 로드맵을 가속화하고, PLP 및 WLP 공정 최적화를 강화하며, 고급 반도체 패키징 솔루션의 수율 달성 시간을 단축하는 장비, 소프트웨어 및 협업 프로세스 환경에 대한 직접 액세스를 제공합니다.

SKU-

세계 최초의 시장 정보 클라우드 보고서에 온라인으로 접속하세요

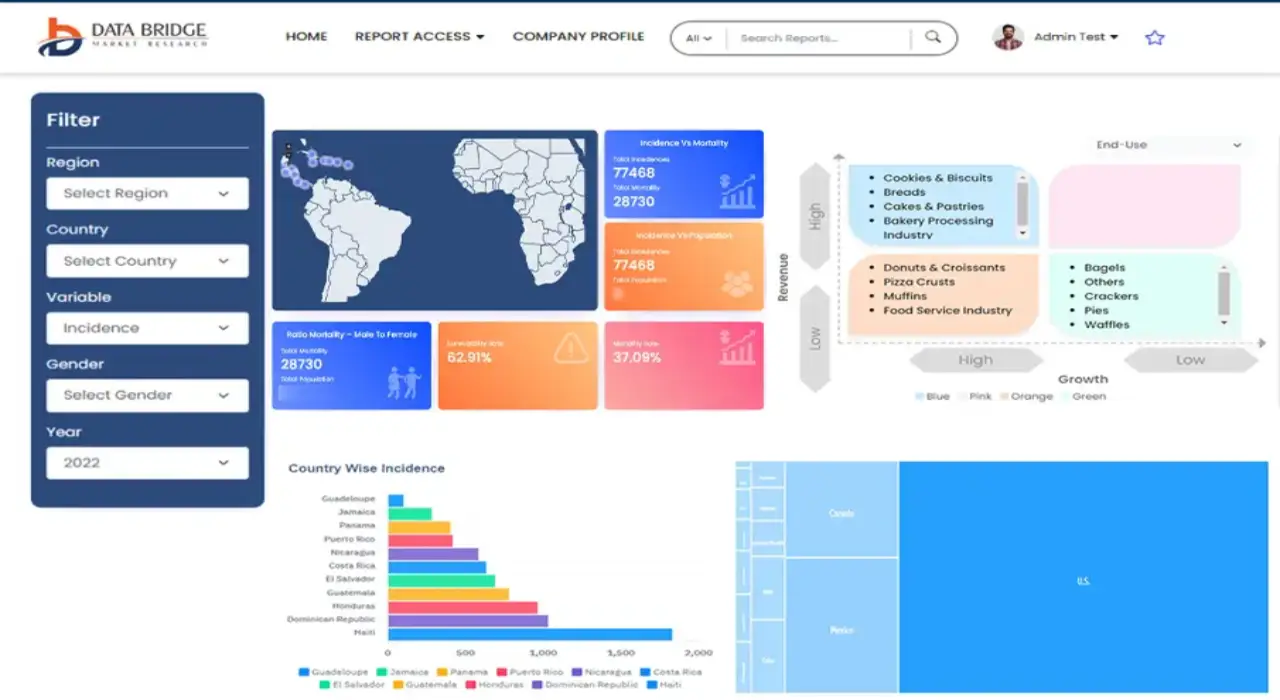

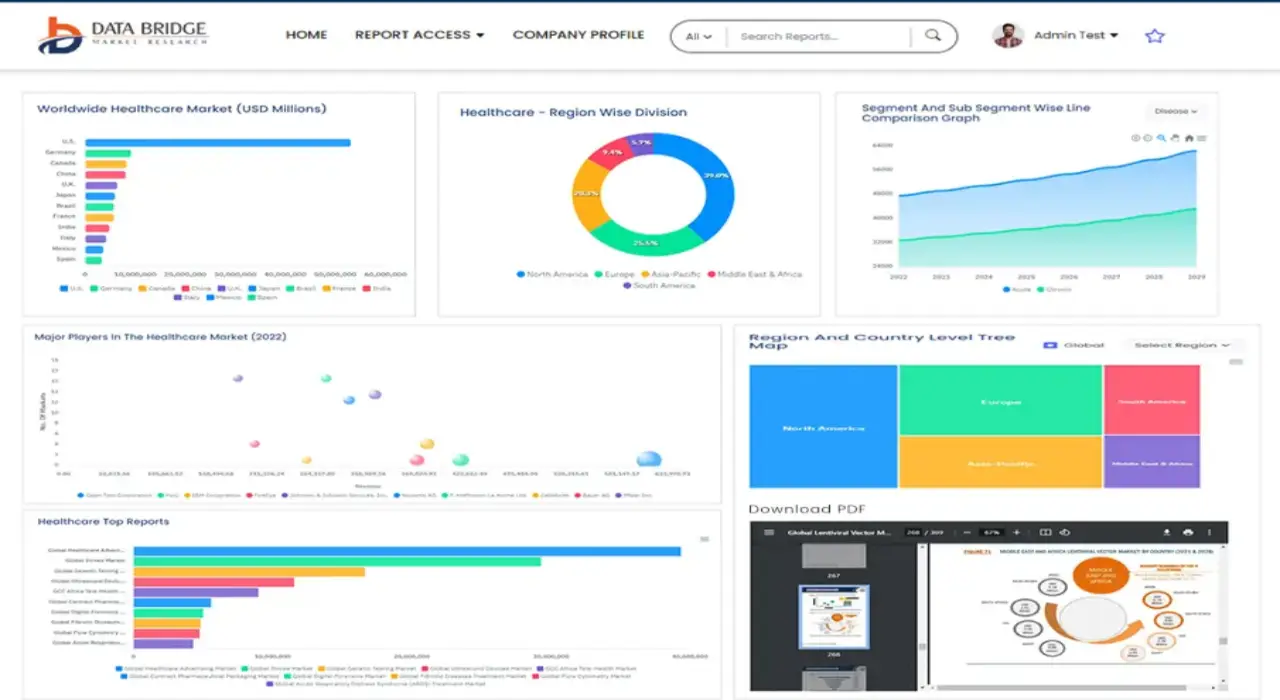

- 대화형 데이터 분석 대시보드

- 높은 성장 잠재력 기회를 위한 회사 분석 대시보드

- 사용자 정의 및 질의를 위한 리서치 분석가 액세스

- 대화형 대시보드를 통한 경쟁자 분석

- 최신 뉴스, 업데이트 및 추세 분석

- 포괄적인 경쟁자 추적을 위한 벤치마크 분석의 힘 활용

연구 방법론

데이터 수집 및 기준 연도 분석은 대규모 샘플 크기의 데이터 수집 모듈을 사용하여 수행됩니다. 이 단계에는 다양한 소스와 전략을 통해 시장 정보 또는 관련 데이터를 얻는 것이 포함됩니다. 여기에는 과거에 수집한 모든 데이터를 미리 검토하고 계획하는 것이 포함됩니다. 또한 다양한 정보 소스에서 발견되는 정보 불일치를 검토하는 것도 포함됩니다. 시장 데이터는 시장 통계 및 일관된 모델을 사용하여 분석하고 추정합니다. 또한 시장 점유율 분석 및 주요 추세 분석은 시장 보고서의 주요 성공 요인입니다. 자세한 내용은 분석가에게 전화를 요청하거나 문의 사항을 드롭하세요.

DBMR 연구팀에서 사용하는 주요 연구 방법론은 데이터 마이닝, 시장에 대한 데이터 변수의 영향 분석 및 주요(산업 전문가) 검증을 포함하는 데이터 삼각 측량입니다. 데이터 모델에는 공급업체 포지셔닝 그리드, 시장 타임라인 분석, 시장 개요 및 가이드, 회사 포지셔닝 그리드, 특허 분석, 가격 분석, 회사 시장 점유율 분석, 측정 기준, 글로벌 대 지역 및 공급업체 점유율 분석이 포함됩니다. 연구 방법론에 대해 자세히 알아보려면 문의를 통해 업계 전문가에게 문의하세요.

사용자 정의 가능

Data Bridge Market Research는 고급 형성 연구 분야의 선두 주자입니다. 저희는 기존 및 신규 고객에게 목표에 맞는 데이터와 분석을 제공하는 데 자부심을 느낍니다. 보고서는 추가 국가에 대한 시장 이해(국가 목록 요청), 임상 시험 결과 데이터, 문헌 검토, 재생 시장 및 제품 기반 분석을 포함하도록 사용자 정의할 수 있습니다. 기술 기반 분석에서 시장 포트폴리오 전략에 이르기까지 타겟 경쟁업체의 시장 분석을 분석할 수 있습니다. 귀하가 원하는 형식과 데이터 스타일로 필요한 만큼 많은 경쟁자를 추가할 수 있습니다. 저희 분석가 팀은 또한 원시 엑셀 파일 피벗 테이블(팩트북)로 데이터를 제공하거나 보고서에서 사용 가능한 데이터 세트에서 프레젠테이션을 만드는 데 도움을 줄 수 있습니다.