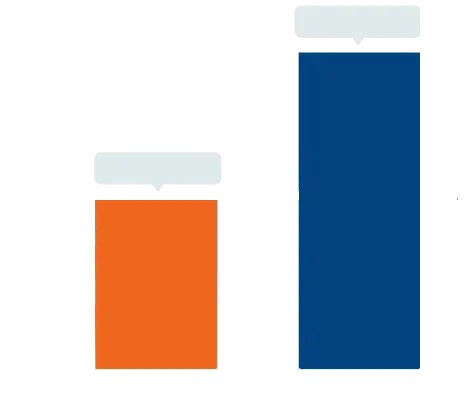

Global Wafer Level Packaging Market

Tamanho do mercado em biliões de dólares

CAGR :

%

USD

10.43 Billion

USD

47.92 Billion

2025

2033

USD

10.43 Billion

USD

47.92 Billion

2025

2033

| 2026 –2033 | |

| USD 10.43 Billion | |

| USD 47.92 Billion | |

|

|

|

|

Segmentação do Mercado Global de Wafer Level Packaging por Integração (Dispositivo Passivo Integrado, Fan-in WLP, Fan-out WLP e Through-Silicon Via), Tecnologia (Flip Chip, Compliant WLP, Chip Scale Package Convencional, Wafer Level Chip Scale Package, Nano Wafer Level Packaging e 3D Wafer Level Packaging), Aplicação (Eletrônica, TI e Telecomunicações, Industrial, Automotivo, Aeroespacial e Defesa, Saúde e Outros), Tecnologia de Bumping (Copper Pillar, Solder Bumping, Gold Bumping e Outros) - Tendências e Previsões do Setor até 2033

Tamanho do mercado de embalagens em nível de wafer

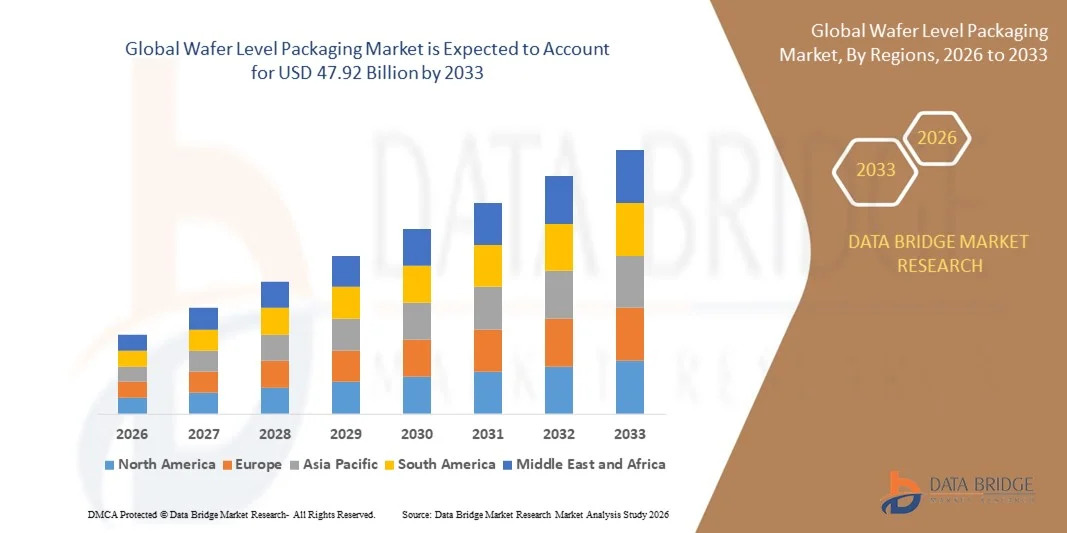

- O mercado global de embalagens em nível de wafer foi avaliado em US$ 10,43 bilhões em 2025 e deverá atingir US$ 47,92 bilhões até 2033 , com uma taxa de crescimento anual composta (CAGR) de 21,0% durante o período de previsão.

- O crescimento do mercado é impulsionado principalmente pela crescente demanda por dispositivos semicondutores compactos, de alto desempenho e com eficiência energética em aplicações de eletrônicos de consumo, automotivas e industriais, incentivando os fabricantes a adotarem métodos avançados de encapsulamento em nível de wafer para aprimorar a funcionalidade e reduzir o tamanho.

- Além disso, o aumento da produção de smartphones, wearables e dispositivos IoT está acelerando a necessidade de melhor desempenho térmico, maior densidade de entrada/saída e características elétricas superiores, tornando a tecnologia de encapsulamento em nível de wafer essencial para sistemas eletrônicos de próxima geração.

Análise do mercado de embalagens em nível de wafer

- A tecnologia de encapsulamento em nível de wafer, que permite a integração de múltiplas funções no próprio wafer, está se tornando crucial para a fabricação moderna de semicondutores devido à sua capacidade de proporcionar maior miniaturização, confiabilidade aprimorada e desempenho elétrico otimizado para uma ampla gama de dispositivos de uso final.

- A crescente demanda por encapsulamento em nível de wafer é impulsionada principalmente pelos rápidos avanços em comunicação móvel, tecnologias de sensores e eletrônica com inteligência artificial, juntamente com a mudança global para componentes semicondutores menores, mais rápidos e mais eficientes, necessários nos setores de consumo, automotivo e industrial.

- A região Ásia-Pacífico dominou o mercado de embalagens em nível de wafer com uma participação de 52,5% em 2025, devido à forte presença de polos de fabricação de semicondutores, à crescente adoção de embalagens avançadas em eletrônicos de consumo e à expansão dos ecossistemas de manufatura nas principais economias.

- A América do Norte deverá ser a região de crescimento mais rápido no mercado de embalagens em nível de wafer durante o período de previsão, devido à crescente demanda por semicondutores de alto desempenho em eletrônicos de consumo, data centers, eletrônicos automotivos e dispositivos baseados em inteligência artificial.

- O segmento de dispositivos passivos integrados (IPDs) dominou o mercado em 2025, impulsionado pela crescente adoção em smartphones, wearables e aplicações de radiofrequência (RF) que exigem componentes miniaturizados e de alto desempenho. Os IPDs permitem desempenho elétrico superior, redução de capacitâncias parasitas e maior integridade de sinal, tornando-os essenciais em dispositivos de comunicação de alta frequência. Sua capacidade de consolidar múltiplas funções passivas em um formato compacto impulsiona sua forte adoção em eletrônicos de consumo e módulos sem fio. Os fabricantes também preferem os IPDs por suportarem produção em larga escala com excelente custo-benefício. A crescente integração de padrões de comunicação avançados, como o 5G, aumenta ainda mais a demanda por soluções WLP baseadas em IPDs em arquiteturas eletrônicas compactas.

Escopo do relatório e segmentação do mercado de embalagens em nível de wafer

|

Atributos |

Principais informações de mercado sobre embalagens em nível de wafer |

|

Segmentos abrangidos |

|

|

Países abrangidos |

América do Norte

Europa

Ásia-Pacífico

Oriente Médio e África

Ámérica do Sul

|

|

Principais participantes do mercado |

|

|

Oportunidades de mercado |

|

|

Conjuntos de informações de dados de valor agregado |

Além das informações sobre cenários de mercado, como valor de mercado, taxa de crescimento, segmentação, cobertura geográfica e principais participantes, os relatórios de mercado elaborados pela Data Bridge Market Research também incluem análise de importação e exportação, visão geral da capacidade de produção, análise de produção e consumo, análise de tendências de preços, cenário de mudanças climáticas, análise da cadeia de suprimentos, análise da cadeia de valor, visão geral de matérias-primas/insumos, critérios de seleção de fornecedores, análise PESTLE, análise de Porter e estrutura regulatória. |

Tendências do mercado de embalagens em nível de wafer

Adoção crescente de tecnologias avançadas de fan-out e encapsulamento em nível de wafer 3D.

- O mercado de encapsulamento em nível de wafer está passando por uma forte mudança em direção a arquiteturas avançadas de fan-out e 3D, à medida que os fabricantes priorizam maior desempenho e densidade de integração para dispositivos semicondutores de próxima geração. Essa tendência é moldada pela crescente necessidade de melhor desempenho elétrico, formatos mais finos e maior eficiência térmica em aplicações como smartphones, computação de alto desempenho e eletrônica automotiva.

- Por exemplo, a Deca Technologies expandiu suas capacidades de encapsulamento fan-out para dar suporte aos principais fabricantes de semicondutores que buscam maior produtividade e flexibilidade de design aprimorada para arquiteturas de chips complexas, demonstrando como os participantes do setor estão acelerando a inovação por meio de plataformas fan-out escaláveis.

- As tecnologias de fan-out e encapsulamento 3D em nível de wafer permitem interconexões mais curtas, maior densidade de E/S e melhor integração do sistema em pacote (SoP), tornando-as essenciais para processadores avançados, aceleradores de IA e dispositivos de computação de borda que exigem designs compactos com alta eficiência energética. Essa mudança é ainda impulsionada pela crescente otimização da fabricação para aprimorar o desempenho e, ao mesmo tempo, controlar os custos.

- A demanda por integração heterogênea está impulsionando a adoção dessas abordagens avançadas de WLP (Wireless Line Projection), à medida que os fabricantes de chips integram múltiplas funções, como memória, lógica e componentes de RF, em encapsulamentos compactos. Essa tendência também é impulsionada pela necessidade de suportar os limites de escalabilidade das arquiteturas 2D tradicionais.

- As empresas estão focando na expansão da capacidade de produção e no fortalecimento da pesquisa e desenvolvimento para tecnologias de encapsulamento de próxima geração, o que está acelerando a adoção de estruturas fan-out e 3D em diversas aplicações de microeletrônica. Esse foco está transformando as expectativas de desempenho e miniaturização no encapsulamento de semicondutores.

- A crescente ênfase em alcançar maior funcionalidade do sistema em espaços menores está impulsionando os fabricantes em direção a embalagens avançadas em nível de wafer (WLE), consolidando a tendência com forte impulso para a adoção contínua nos mercados de eletrônicos de consumo, automotivo e computação de alto desempenho.

Dinâmica do mercado de embalagens em nível de wafer

Motorista

Crescente demanda por dispositivos semicondutores miniaturizados e de alto desempenho.

- A crescente demanda de consumidores e da indústria por dispositivos semicondutores compactos, com baixo consumo de energia e alto desempenho está impulsionando a forte adoção de soluções de encapsulamento em nível de wafer (WLP) em diversas aplicações. À medida que os dispositivos eletrônicos se tornam menores e mais avançados, o WLP oferece a densidade, a velocidade e a confiabilidade necessárias para as arquiteturas de chips modernas.

- Por exemplo, a Amkor Technology continua expandindo seu portfólio avançado de embalagens em nível de wafer para atender às crescentes necessidades de fabricantes de smartphones e dispositivos de computação que exigem perfis mais finos e maior desempenho funcional.

- As tendências de miniaturização em eletrônicos de consumo, como wearables, nós de IoT e smartphones, estão impulsionando a demanda por soluções de encapsulamento que ofereçam alta densidade de E/S, integridade de sinal aprimorada e latência reduzida. O WLP (Wide Layer Protection) possibilita essas capacidades ao minimizar o comprimento das interconexões e otimizar o caminho elétrico dentro do encapsulamento do chip.

- A crescente expectativa por baixo consumo de energia e funcionalidade aprimorada dos dispositivos está impulsionando os fabricantes a adotarem a tecnologia de encapsulamento em nível de wafer como solução de integração preferencial em aplicações industriais e de consumo. Isso reforça seu papel crucial no desenvolvimento de semicondutores de próxima geração.

- O aumento da demanda por computação de alto desempenho e eletrônica compacta continua a posicionar a tecnologia WLP como essencial, concluindo este estudo com sua importância para viabilizar a miniaturização de chips e avanços de desempenho.

Restrição/Desafio

Alto investimento de capital e requisitos complexos de fabricação

- O mercado de embalagens em nível de wafer enfrenta desafios significativos devido ao alto investimento de capital necessário para infraestrutura de fabricação avançada e à complexidade dos processos de produção associados. A instalação de linhas de fabricação de WLP exige equipamentos caros, ferramentas de precisão e ambientes de sala limpa especializados, criando barreiras para novos entrantes e empresas menores.

- Por exemplo, empresas que investem em ferramentas de litografia, colagem e metrologia de ponta enfrentam compromissos financeiros substanciais, o que pode limitar sua capacidade de expansão rápida. Processos WLP avançados, como fan-out, empilhamento 3D e integração heterogênea, exigem conhecimento especializado em fabricação, alinhamento preciso e técnicas avançadas de manuseio de materiais, o que aumenta a complexidade operacional. Esses requisitos tornam a otimização de processos um grande desafio para muitas instalações de embalagem de semicondutores.

- A necessidade de investimento contínuo em P&D, automação de processos e garantia da qualidade aumenta ainda mais a pressão sobre os custos, especialmente à medida que as tecnologias de embalagem evoluem para suportar níveis de integração mais elevados e dimensões mais precisas. Essa complexidade dificulta a adoção por parte dos fabricantes sensíveis a custos.

- Com o avanço das tecnologias de produção, manter a estabilidade do rendimento e a uniformidade do processo torna-se cada vez mais difícil devido às múltiplas etapas de fabricação e aos maiores riscos de defeitos, contribuindo para os desafios operacionais. Essas questões afetam a escalabilidade e a eficiência de custos.

- A combinação de elevados requisitos de investimento de capital e fluxos de trabalho de fabricação complexos representa um desafio constante para a adoção em larga escala. Concluímos esta seção destacando a importância de abordar as restrições de custo, capacidade e conhecimento especializado em fabricação na expansão da tecnologia WLP.

Escopo do mercado de embalagens em nível de wafer

O mercado é segmentado com base na integração, tecnologia, aplicação e tecnologia de bumping.

- Por integração

Com base na integração, o mercado de encapsulamento em nível de wafer é segmentado em Dispositivo Passivo Integrado (IPD), Fan-In WLP, Fan-Out WLP e Through-Silicon Via (TSV). O segmento de Dispositivo Passivo Integrado dominou o mercado em 2025 devido à sua crescente adoção em smartphones, wearables e aplicações de radiofrequência (RF) que exigem componentes miniaturizados e de alto desempenho. Os IPDs permitem desempenho elétrico superior, redução de capacitâncias parasitas e maior integridade de sinal, tornando-os essenciais em dispositivos de comunicação de alta frequência. Sua capacidade de consolidar múltiplas funções passivas em um formato compacto impulsiona uma forte adoção em eletrônicos de consumo e módulos sem fio. Os fabricantes também preferem os IPDs porque eles suportam produção em alto volume com excelente custo-benefício. A crescente integração de padrões de comunicação avançados, como o 5G, impulsiona ainda mais a demanda por soluções WLP baseadas em IPD em arquiteturas eletrônicas compactas.

O segmento Fan-Out WLP deverá apresentar o crescimento mais rápido entre 2026 e 2033, impulsionado por sua adequação a aplicações que exigem alta densidade de E/S e melhor desempenho térmico e elétrico. O Fan-Out WLP permite a redistribuição de conexões, possibilitando encapsulamentos mais complexos, mantendo um perfil fino, o que o torna popular em processadores móveis de última geração e circuitos integrados de gerenciamento de energia. A tecnologia está sendo cada vez mais adotada em sistemas avançados de assistência ao motorista (ADAS), eletrônicos vestíveis compactos e módulos de IoT que exigem dissipação de calor eficiente e confiabilidade superior. Sua escalabilidade para integração heterogênea a posiciona fortemente dentro da evolução dos projetos de semicondutores. Os desenvolvimentos contínuos por grandes empresas de semicondutores para expandir a capacidade do Fan-Out impulsionam ainda mais sua trajetória de alto crescimento durante o período previsto.

- Por meio da tecnologia

Com base na tecnologia, o mercado é segmentado em Flip Chip, Compliant WLP, Conventional Chip Scale Package (CSP), Wafer Level Chip Scale Package (WLCSP), Nano WLP e 3D WLP. O segmento WLCSP dominou o mercado em 2025 devido à sua ampla adoção em dispositivos móveis, eletrônicos de consumo e sensores automotivos que exigem formatos ultracompactos. O WLCSP oferece benefícios como baixa indutância, excelentes características térmicas, alta confiabilidade e encapsulamento em tamanho de chip real, tornando-o altamente preferido para fabricação em larga escala. A tecnologia suporta características elétricas eficientes, essenciais para dispositivos de RF, gerenciamento de energia e MEMS. O WLCSP também reduz as etapas de processamento e o custo de encapsulamento, impulsionando a integração em larga escala pelos principais fabricantes de semicondutores. Sua compatibilidade com nós avançados garante a continuidade da sua liderança em eletrônica miniaturizada.

Prevê-se que o segmento de encapsulamento em nível de wafer 3D registre o crescimento mais rápido até 2033, devido à crescente necessidade de arquiteturas de empilhamento avançadas que aprimoram o desempenho e a largura de banda. Essa tecnologia suporta a integração vertical de chips, permitindo interconexões mais curtas e velocidades de processamento mais altas, o que é crucial para computação de alto desempenho (HPC), aceleradores de IA e dispositivos de memória de próxima geração. O encapsulamento em nível de wafer 3D oferece escalabilidade excepcional para projetos de semicondutores complexos que exigem maior funcionalidade em tamanhos compactos. A crescente adoção da integração 3D em data centers, eletrônicos de consumo de alto desempenho e eletrônicos automotivos acelera sua implementação. Os avanços contínuos nas tecnologias de interconexão através do silício (TSVI) e de ligação híbrida fortalecem o papel do encapsulamento em nível de wafer 3D no ecossistema de encapsulamento de semicondutores.

- Por meio de aplicação

Com base na aplicação, o mercado de encapsulamento em nível de wafer (WLP) é segmentado em Eletrônica, TI e Telecomunicações, Industrial, Automotivo, Aeroespacial e Defesa, Saúde e Outros. O segmento de Eletrônica dominou o mercado em 2025, impulsionado pelo consumo massivo de smartphones, wearables, tablets e dispositivos de realidade aumentada/virtual (AR/VR) que exigem encapsulamentos de semicondutores compactos e de alto desempenho. A crescente adoção de circuitos integrados e sensores miniaturizados em eletrônicos de consumo fortalece ainda mais a demanda por WLP. O segmento se beneficia significativamente da necessidade de chips de baixo consumo de energia, termicamente eficientes e com custo-benefício em eletrônicos portáteis. As tecnologias WLP permitem funcionalidades aprimoradas em espaço limitado na placa, auxiliando os fabricantes a fornecer dispositivos mais elegantes e de alto desempenho. A inovação contínua em dispositivos de consumo em todo o mundo garante que o segmento de eletrônica mantenha sua posição de liderança.

Prevê-se que o segmento automotivo apresente o crescimento mais rápido entre 2026 e 2033, devido ao aumento do conteúdo eletrônico em veículos modernos, incluindo ADAS, sistemas de infoentretenimento, eletrônica de potência e plataformas para veículos elétricos. As aplicações automotivas exigem soluções de encapsulamento robustas e de alta confiabilidade, capazes de suportar temperaturas extremas e níveis de vibração, tornando a tecnologia WLP uma opção atraente. A transição para a eletrificação de veículos e a mobilidade autônoma requer componentes semicondutores avançados que ofereçam eficiência e desempenho de processamento superiores. A tecnologia WLP suporta a integração compacta de sensores, microcontroladores e circuitos integrados de gerenciamento de energia, essenciais nas arquiteturas automotivas de próxima geração. Os crescentes investimentos de montadoras e fornecedores de nível 1 em tecnologias semicondutoras avançadas impulsionam ainda mais o crescimento do segmento.

- Por meio da tecnologia de impacto

Com base na tecnologia de interconexão por esferas (bumping), o mercado é segmentado em Pilar de Cobre, Interconexão por Esferas de Solda, Interconexão por Esferas de Ouro e Outros. O segmento de Interconexão por Esferas de Solda dominou o mercado em 2025 devido à sua maturidade, custo-benefício e ampla utilização em diversos dispositivos semicondutores. As interconexões por esferas de solda proporcionam conexões elétricas e mecânicas confiáveis para encapsulamento flip-chip e em nível de wafer, tornando-as ideais para a fabricação em larga escala. O método oferece fortes características térmicas e compatibilidade com diversas aplicações, incluindo processadores móveis, memória e componentes de RF. Sua cadeia de suprimentos e infraestrutura de fabricação consolidadas reforçam ainda mais sua posição de liderança. A tecnologia continua sendo a escolha preferida para equilibrar desempenho, custo e eficiência de fabricação na produção convencional de semicondutores.

Prevê-se que o segmento de interconexões por pilares de cobre registre o crescimento mais rápido durante o período de previsão, devido à sua capacidade superior de condução de corrente, melhor desempenho térmico e escalabilidade de passo fino. A interconexões por pilares de cobre está sendo cada vez mais utilizada em dispositivos de alta densidade e alto desempenho, como chips lógicos avançados, processadores de IA e memórias de alta largura de banda. A tecnologia suporta interconexões mais finas e melhor resistência à eletromigração, tornando-a adequada para arquiteturas semicondutoras compactas modernas. À medida que métodos avançados de encapsulamento, como a integração 2.5D e 3D, se expandem, a interconexões por pilares de cobre torna-se ainda mais crucial. A crescente adoção em eletrônicos automotivos, data centers e eletrônicos de consumo premium acelera seu crescimento até 2033.

Análise Regional do Mercado de Embalagem em Nível de Wafer

- A região Ásia-Pacífico dominou o mercado de embalagens em nível de wafer, com a maior participação na receita, de 52,5% em 2025, impulsionada pela forte presença de polos de fabricação de semicondutores, pela crescente adoção de embalagens avançadas em eletrônicos de consumo e pela expansão dos ecossistemas de manufatura nas principais economias.

- A capacidade de produção economicamente viável da região, os crescentes investimentos em tecnologias de nível de wafer e o rápido crescimento na fabricação de hardware para dispositivos móveis e IoT estão acelerando a expansão geral do mercado.

- A disponibilidade de profissionais de engenharia qualificados, as iniciativas governamentais de apoio ao desenvolvimento de semicondutores e o consumo em larga escala de eletrônicos em economias emergentes estão contribuindo para a adoção substancial da tecnologia de encapsulamento em nível de wafer.

Análise do Mercado de Embalagem em Nível de Wafer na China

Em 2025, a China detinha a maior participação no mercado de embalagens em nível de wafer na região Ásia-Pacífico, devido à sua posição dominante na montagem de semicondutores, testes e produção de eletrônicos de consumo. A expansão da capacidade de produção de semicondutores no país, o forte apoio governamental por meio de programas de autossuficiência em semicondutores e o crescente foco em tecnologias avançadas de embalagem são os principais impulsionadores desse crescimento. A demanda é ainda sustentada pela produção em larga escala de smartphones, dispositivos vestíveis e processadores de alto desempenho para os mercados doméstico e global.

Análise do Mercado de Embalagem em Nível de Wafer na Índia

A Índia está testemunhando o crescimento mais rápido na região Ásia-Pacífico, impulsionado por investimentos crescentes em instalações de montagem e teste de semicondutores, pela demanda cada vez maior por embalagens avançadas em smartphones e eletrônicos automotivos e por incentivos governamentais à fabricação de semicondutores. A iniciativa “Make in India” e o crescente interesse de fabricantes globais de chips estão fortalecendo a adoção da tecnologia de embalagens em nível de wafer. A expansão da fabricação nacional de eletrônicos e o rápido crescimento no consumo de dispositivos eletrônicos também contribuem para o forte dinamismo do mercado.

Análise do Mercado Europeu de Embalagem em Nível de Wafer

O mercado europeu de embalagens em nível de wafer está em constante expansão, impulsionado pela forte demanda por soluções avançadas de semicondutores em eletrônica automotiva, automação industrial e aplicações de alta confiabilidade. A região prioriza a fabricação de alta qualidade, padrões regulatórios rigorosos e avanços tecnológicos em microeletrônica de alto desempenho. A crescente adoção de dispositivos miniaturizados, os investimentos contínuos em P&D e a necessidade cada vez maior de embalagens eficientes para sensores e eletrônica de potência estão impulsionando ainda mais o crescimento do mercado.

Análise do mercado de embalagens em nível de wafer na Alemanha

O mercado alemão de embalagens em nível de wafer é impulsionado por sua liderança em eletrônica automotiva, máquinas industriais avançadas e fabricação de semicondutores de precisão. A forte infraestrutura de P&D do país, as colaborações entre centros de pesquisa acadêmica e empresas de semicondutores, e a demanda por componentes de alta confiabilidade em aplicações automotivas e industriais são fatores-chave. A crescente integração de sensores, dispositivos de potência e microcontroladores em veículos de última geração apoia a adoção de embalagens avançadas.

Análise do Mercado de Embalagem em Nível de Wafer no Reino Unido

O mercado do Reino Unido é sustentado por um ecossistema maduro de design eletrônico, esforços contínuos para fortalecer a resiliência da cadeia de suprimentos de semicondutores e investimentos crescentes em pesquisa avançada para microeletrônica e nanofabricação. A forte colaboração entre academia e indústria, o crescimento da inovação em eletrônica médica e o foco no desenvolvimento de semicondutores de alto valor agregado continuam a reforçar o papel do Reino Unido em tecnologias de encapsulamento especializadas. A demanda é particularmente forte em instrumentação para ciências da vida, dispositivos de comunicação e sistemas industriais.

Análise do Mercado de Embalagem em Nível de Wafer na América do Norte

Prevê-se que a América do Norte apresente o crescimento anual composto mais rápido entre 2026 e 2033, impulsionada pela crescente demanda por semicondutores de alto desempenho em eletrônicos de consumo, data centers, eletrônicos automotivos e dispositivos com inteligência artificial. A região se beneficia de recursos de P&D de ponta, forte presença de empresas líderes em semicondutores fabless e rápida adoção de tecnologias de encapsulamento de wafers 3D e avançadas. O aumento da relocalização da produção de semicondutores e os grandes investimentos federais na fabricação de chips também estão acelerando a expansão do mercado.

Análise do Mercado de Embalagem em Nível de Wafer nos EUA

Os EUA detiveram a maior participação no mercado de embalagens em nível de wafer da América do Norte em 2025, impulsionados por seu forte ecossistema de inovação em semicondutores, programas avançados de P&D em embalagens e significativa capacidade de produção para computação de alto desempenho, dispositivos de comunicação e eletrônica automotiva. A ênfase do país na liderança tecnológica, o robusto investimento em design de chips e a presença de grandes fabricantes e fundições de semicondutores contribuem para a forte demanda por embalagens em nível de wafer. A crescente integração de IA, computação em nuvem e eletrônica para veículos elétricos fortalece ainda mais a posição dos EUA no mercado regional.

Participação de mercado de embalagens em nível de wafer

O setor de embalagens em nível de wafer é liderado principalmente por empresas consolidadas, incluindo:

- JCET Group Co., Ltd. (China)

- NEMOTEK Tecnologia (Marrocos)

- Corporação de Tecnologia Chipbond (Taiwan)

- Fujitsu (Japão)

- Powertech Technology Inc. (Taiwan)

- China Wafer Level CSP Co., Ltd. (China)

- Indústrias de Precisão de Silício Co., Ltda. (Taiwan)

- Amkor Technology (EUA)

- IQE PLC (Reino Unido)

- ChipMOS Technologies Inc. (Taiwan)

- Deca Technologies (EUA)

- Qualcomm Technologies, Inc. (EUA)

- Toshiba Corporation (Japão)

- Tokyo Electron Limited (Japão)

- Applied Materials, Inc. (EUA)

- Corporação de Pesquisa Lam (EUA)

- ASML (Países Baixos)

- Infineon Technologies AG (Alemanha)

- KLA Corporation (EUA)

- Marvell (EUA)

Últimos desenvolvimentos no mercado global de embalagens em nível de wafer

- Em setembro de 2024, a Samsung Electronics anunciou uma grande expansão de seu ecossistema de embalagens avançadas, integrando recursos aprimorados de embalagem em nível de wafer e montagem de chiplets em suas fábricas na Coreia do Sul. Essa iniciativa fortalece sua posição em integração heterogênea, atende à crescente demanda por embalagens de semicondutores de alta densidade em aplicações de IA e HPC e acelera a adoção de tecnologias WLP de próxima geração, melhorando a eficiência da produção e reduzindo os ciclos de desenvolvimento.

- Em agosto de 2024, a ASE Technology Holding revelou planos para modernizar suas unidades de produção em Taiwan com plataformas de teste em nível de wafer de última geração e sistemas de automação avançados. Esse investimento aprimora a estabilidade da produção, suporta maiores volumes de soluções WLP compactas e confiáveis e fortalece a capacidade da empresa de atender à crescente demanda dos setores de eletrônica automotiva, dispositivos IoT e aplicações avançadas para o consumidor.

- Em março de 2024, a Universidade Estadual do Arizona e a Deca Technologies firmaram uma parceria para estabelecer o primeiro centro de pesquisa e desenvolvimento dedicado à tecnologia de encapsulamento em nível de wafer com tecnologia fan-out (FOWLP) na América do Norte. Essa colaboração eleva a liderança tecnológica dos EUA em encapsulamento avançado, acelera a inovação em arquiteturas FOWLP e fortalece a resiliência da cadeia de suprimentos de semicondutores do país, fomentando o desenvolvimento conjunto entre indústria e academia de processos de próxima geração.

- Em março de 2024, a Taiwan Semiconductor Manufacturing Company Limited anunciou seu plano de expansão da capacidade de encapsulamento de chips avançados no Japão, como parte de sua estratégia global de escalonamento. Essa expansão aprimora a capacidade de produção regional, fortalece a diversificação da cadeia de suprimentos e atende à crescente demanda por tecnologias de encapsulamento em nível de wafer, utilizadas em dispositivos de alto desempenho e aplicações lógicas avançadas.

- Em junho de 2023, a Onto Innovation lançou seu Centro de Excelência em Aplicações para embalagens em nível de painel em sua sede em Wilmington, Massachusetts. Essa instalação oferece aos clientes acesso direto a equipamentos, softwares e ambientes de processo colaborativos que aceleram os roteiros tecnológicos, aprimoram a otimização dos processos de PLP e WLP e reduzem o tempo de produção de soluções avançadas de embalagens de semicondutores.

SKU-

Obtenha acesso online ao relatório sobre a primeira nuvem de inteligência de mercado do mundo

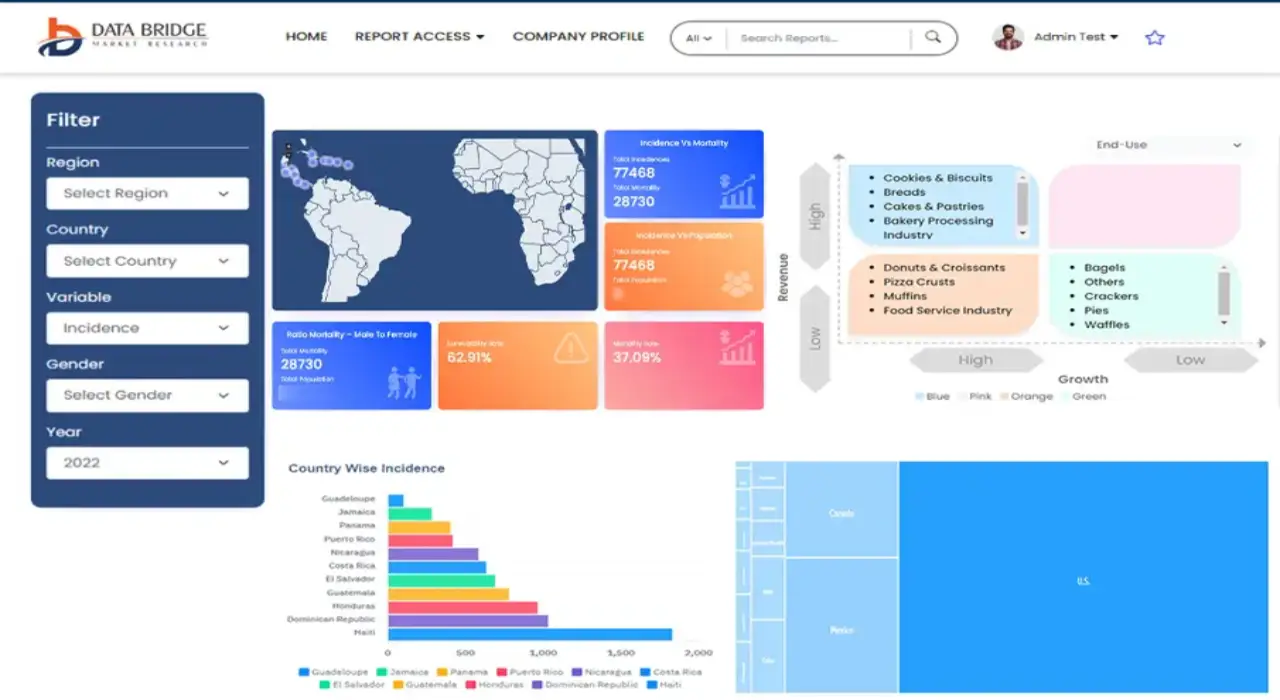

- Painel interativo de análise de dados

- Painel de análise da empresa para oportunidades de elevado potencial de crescimento

- Acesso de analista de pesquisa para personalização e customização. consultas

- Análise da concorrência com painel interativo

- Últimas notícias, atualizações e atualizações Análise de tendências

- Aproveite o poder da análise de benchmark para um rastreio abrangente da concorrência

Metodologia de Investigação

A recolha de dados e a análise do ano base são feitas através de módulos de recolha de dados com amostras grandes. A etapa inclui a obtenção de informações de mercado ou dados relacionados através de diversas fontes e estratégias. Inclui examinar e planear antecipadamente todos os dados adquiridos no passado. Da mesma forma, envolve o exame de inconsistências de informação observadas em diferentes fontes de informação. Os dados de mercado são analisados e estimados utilizando modelos estatísticos e coerentes de mercado. Além disso, a análise da quota de mercado e a análise das principais tendências são os principais fatores de sucesso no relatório de mercado. Para saber mais, solicite uma chamada de analista ou abra a sua consulta.

A principal metodologia de investigação utilizada pela equipa de investigação do DBMR é a triangulação de dados que envolve a mineração de dados, a análise do impacto das variáveis de dados no mercado e a validação primária (especialista do setor). Os modelos de dados incluem grelha de posicionamento de fornecedores, análise da linha de tempo do mercado, visão geral e guia de mercado, grelha de posicionamento da empresa, análise de patentes, análise de preços, análise da quota de mercado da empresa, normas de medição, análise global versus regional e de participação dos fornecedores. Para saber mais sobre a metodologia de investigação, faça uma consulta para falar com os nossos especialistas do setor.

Personalização disponível

A Data Bridge Market Research é líder em investigação formativa avançada. Orgulhamo-nos de servir os nossos clientes novos e existentes com dados e análises que correspondem e atendem aos seus objetivos. O relatório pode ser personalizado para incluir análise de tendências de preços de marcas-alvo, compreensão do mercado para países adicionais (solicite a lista de países), dados de resultados de ensaios clínicos, revisão de literatura, mercado remodelado e análise de base de produtos . A análise de mercado dos concorrentes-alvo pode ser analisada desde análises baseadas em tecnologia até estratégias de carteira de mercado. Podemos adicionar quantos concorrentes necessitar de dados no formato e estilo de dados que procura. A nossa equipa de analistas também pode fornecer dados em tabelas dinâmicas de ficheiros Excel em bruto (livro de factos) ou pode ajudá-lo a criar apresentações a partir dos conjuntos de dados disponíveis no relatório.