Global 3d Semiconductor Packaging Market

Marktgröße in Milliarden USD

CAGR :

%

USD

14.39 Million

USD

46.21 Million

2025

2033

USD

14.39 Million

USD

46.21 Million

2025

2033

| 2026 –2033 | |

| USD 14.39 Million | |

| USD 46.21 Million | |

|

|

|

|

Globale Marktsegmentierung für 3D-Halbleitergehäuse nach Technologie (3D-Durchkontaktierung, 3D-Package-on-Package, 3D-Fan-Out-basiert, 3D-Drahtbonden), Material (organisches Substrat, Bonddraht, Leadframe, Vergussmasse, Keramikgehäuse, Die-Attach-Material) und Branche (Elektronik, Industrie, Automobil & Transport, Gesundheitswesen, IT & Telekommunikation, Luft- & Raumfahrt) – Branchentrends und Prognose bis 2033

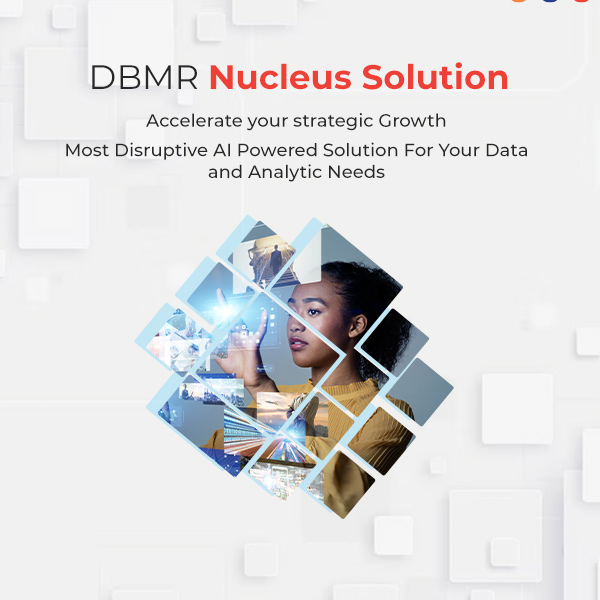

Globale Marktgröße für 3D-Halbleiterverpackungen

- Der globale Markt für 3D-Halbleiterverpackungen hatte im Jahr 2025 einen Wert von 14,39 Millionen US-Dollar und wird voraussichtlich bis 2033 auf 46,21 Millionen US-Dollar anwachsen , was einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 15,70 % im Prognosezeitraum entspricht.

- Das Marktwachstum wird primär durch die steigende Nachfrage nach miniaturisierten elektronischen Geräten, leistungsfähigeren Computern und fortschrittlichen Speicherlösungen angetrieben, die innovative Gehäusetechnologien erfordern, um Effizienz und Funktionalität zu verbessern.

- Darüber hinaus treibt die zunehmende Verbreitung von KI, IoT und Hochleistungsrechnern in verschiedenen Branchen den Bedarf an zuverlässigen, hochdichten und energieeffizienten Halbleitergehäusen an. Diese Faktoren treiben gemeinsam die Expansion des Marktes für 3D-Halbleitergehäuse voran und tragen somit maßgeblich zu dessen starkem Wachstum bei.

Globale Marktanalyse für 3D-Halbleitergehäuse

- Die 3D-Halbleitergehäusetechnologie, die das vertikale Stapeln von Chips und fortschrittliche Verbindungslösungen ermöglicht, entwickelt sich aufgrund ihrer Fähigkeit, die Leistung zu steigern, den Formfaktor zu reduzieren und die Energieeffizienz bei Computern, Speichern und Mobilgeräten zu verbessern, zu einer Schlüsseltechnologie in der modernen Elektronik.

- Die zunehmende Verbreitung von Hochleistungsrechnern, KI, IoT und fortschrittlichen Speichertechnologien treibt die Nachfrage nach 3D-Halbleitergehäusen an, da diese Anwendungen höhere Bandbreite, geringere Latenz und kompaktere Integrationslösungen erfordern.

- Der asiatisch-pazifische Raum dominierte den globalen Markt für 3D-Halbleiterverpackungen mit dem größten Umsatzanteil von 32,2 % im Jahr 2025. Unterstützt wurde dies durch ein starkes Ökosystem der Halbleiterindustrie, die frühzeitige Einführung fortschrittlicher Verpackungstechnologien und erhebliche Investitionen führender Chiphersteller, die sich auf Hochleistungsrechnen und KI-Anwendungen konzentrieren.

- Nordamerika dürfte im Prognosezeitraum die am schnellsten wachsende Region im globalen Markt für 3D-Halbleiterverpackungen sein. Treiber dieser Entwicklung sind die rasche Urbanisierung, die Ausweitung der Elektronikfertigung, die zunehmende Verbreitung von Smartphones und Unterhaltungselektronik sowie die wachsenden Investitionen in Forschung und Entwicklung im Bereich fortschrittlicher Verpackungslösungen.

- Das Segment der 3D-TSVs dominierte den Markt mit dem größten Umsatzanteil von 45,6 % im Jahr 2025. Ausschlaggebend hierfür war die Fähigkeit des Segments, hochdichte Verbindungen, eine überlegene thermische Leistung und eine verbesserte Signalintegrität für Hochleistungsrechner, KI und Speicheranwendungen bereitzustellen.

Berichtsumfang und globale Marktsegmentierung für 3D-Halbleitergehäuse

|

Attribute |

Wichtigste Markteinblicke in die 3D-Halbleiterverpackung. |

|

Abgedeckte Segmente |

|

|

Abgedeckte Länder |

Nordamerika

Europa

Asien-Pazifik

Naher Osten und Afrika

Südamerika

|

|

Wichtige Marktteilnehmer |

|

|

Marktchancen |

|

|

Mehrwertdaten-Infosets |

Zusätzlich zu den Erkenntnissen über Marktszenarien wie Marktwert, Wachstumsrate, Segmentierung, geografische Abdeckung und Hauptakteure enthalten die von Data Bridge Market Research erstellten Marktberichte auch Import-Export-Analysen, einen Überblick über die Produktionskapazität, eine Analyse des Produktionsverbrauchs, eine Preistrendanalyse, ein Klimawandelszenario, eine Lieferkettenanalyse, eine Wertschöpfungskettenanalyse, einen Überblick über Rohstoffe/Verbrauchsmaterialien, Kriterien für die Lieferantenauswahl, eine PESTLE-Analyse, eine Porter-Analyse und den regulatorischen Rahmen. |

Globale Markttrends für 3D-Halbleiterverpackungen

Verbesserte Leistung durch 3D-Integration und KI-optimiertes Design

- Ein bedeutender und sich beschleunigender Trend auf dem globalen Markt für 3D-Halbleitergehäuse ist die zunehmende Integration von 3D-Gehäusetechnologien mit KI-optimierten Chipdesigns und Hochleistungsrechnerarchitekturen. Diese Kombination verbessert die Geräteperformance, die Energieeffizienz und das Wärmemanagement signifikant.

- Beispielsweise ermöglichen die 3D-Packaging-Lösungen CoWoS (Chip-on-Wafer-on-Substrate) und InFO (Integrated Fan-Out) von TSMC hochdichte Verbindungen und eine verbesserte Signalintegrität. Dadurch erzielen KI-Beschleuniger und GPUs eine überragende Rechenleistung in kompakten Formfaktoren. Intels Foveros-3D-Stapeltechnologie ermöglicht die vertikale Integration von Logik- und Speicherschichten und sorgt so für höhere Verarbeitungseffizienz und geringere Latenz.

- KI-gestützte Designwerkzeuge ermöglichen intelligentere 3D-Gehäuselayouts und optimieren die Wärmeableitung, das Signalrouting und die Stromverteilung. So unterstützt beispielsweise fortschrittliche Modellierungssoftware von Cadence und Synopsys Halbleiterhersteller bei der Vorhersage der Wärmeableitung und der Verbesserung der Verbindungseffizienz in 3D-gestapelten Chips. Dies ermöglicht eine höhere Leistung für Anwendungen wie Rechenzentren, KI-Computing und Edge-Geräte.

- Die nahtlose Integration von 3D-Packaging und KI-optimierten Chipdesigns ermöglicht die Entwicklung kompakterer, energieeffizienterer und bandbreitenstärkerer Geräte. Halbleiterunternehmen können so die Rechenleistung steigern und gleichzeitig die Baugröße reduzieren, was Anwendungen in mobilen Geräten, HPC-Systemen und IoT-Plattformen zugutekommt.

- Dieser Trend hin zu intelligenteren, effizienteren und kompakteren Gehäuselösungen verändert grundlegend die Erwartungen an Chip-Leistung und Skalierbarkeit. Unternehmen wie Intel, Samsung und ASE entwickeln daher fortschrittliche 3D-Halbleitergehäuse, die hochdichte Verbindungen mit KI-gestützter Optimierung kombinieren, um den wachsenden Anforderungen moderner Elektronik gerecht zu werden.

- Die Nachfrage nach 3D-Halbleitergehäuselösungen, die KI-optimierte Designs unterstützen, wächst rasant sowohl im Bereich der Unterhaltungselektronik als auch im Bereich der Unternehmens-IT, da die Hersteller zunehmend Wert auf Leistung, Energieeffizienz und Miniaturisierung legen.

Dynamik des globalen Marktes für 3D-Halbleitergehäuse

Treiber

Wachsender Bedarf aufgrund der Nachfrage nach leistungsstarker und miniaturisierter Elektronik

- Die steigende Nachfrage nach Hochleistungsrechnern, KI-Anwendungen und kompakten elektronischen Geräten ist ein wesentlicher Treiber für die verstärkte Nutzung von 3D-Halbleitergehäuselösungen.

- So erweiterte TSMC beispielsweise im Jahr 2025 seine CoWoS- und InFO-3D-Gehäuseproduktion, um dem steigenden Bedarf an fortschrittlichen KI-Beschleunigern und Speichermodulen mit hoher Bandbreite gerecht zu werden. Solche strategischen Initiativen führender Unternehmen dürften das Marktwachstum im gesamten Prognosezeitraum vorantreiben.

- Da Elektronikhersteller bestrebt sind, die Chip-Performance zu verbessern und gleichzeitig Platzbedarf und Stromverbrauch zu reduzieren, bietet die 3D-Halbleitergehäusetechnologie fortschrittliche Funktionen wie hochdichte Verbindungen, verbessertes Wärmemanagement und reduzierte Signalverzögerung und stellt somit eine überzeugende Alternative zur herkömmlichen 2D-Gehäusetechnologie dar.

- Darüber hinaus macht die zunehmende Verbreitung von IoT-, Unterhaltungselektronik- und Rechenzentrumslösungen die 3D-Gehäusetechnologie zu einer unverzichtbaren Technologie für das moderne Halbleiterdesign, da sie die nahtlose Integration von Speicher-, Logik- und Leistungsschichten in einem einzigen kompakten Gehäuse ermöglicht.

- Der Bedarf an schnelleren und energieeffizienteren Geräten sowie der Trend zu miniaturisierter Unterhaltungselektronik und HPC-Systemen treiben die Einführung von 3D-Packaging in zahlreichen Branchen voran. Steigende Investitionen in Forschung und Entwicklung sowie die Verfügbarkeit modularer und skalierbarer 3D-Packaging-Optionen tragen zusätzlich zum Marktwachstum bei.

Zurückhaltung/Herausforderung

Technische Komplexität und hohe Herstellungskosten

- Die technische Komplexität und die vergleichsweise hohen Herstellungskosten von 3D-Halbleitergehäusen stellen erhebliche Herausforderungen für eine breitere Marktakzeptanz dar. Fortschrittliche Stapelverfahren, Durchkontaktierungen (TSVs) und präzise Ausrichtungsanforderungen erhöhen den Produktionsaufwand und die Kosten im Vergleich zu herkömmlichen Gehäusemethoden.

- Kleinere Halbleiterhersteller könnten beispielsweise die Implementierung von Foveros- oder CoWoS-3D-Packaging als schwierig empfinden, da dafür spezielle Ausrüstung und Fachkenntnisse erforderlich sind.

- Die Bewältigung dieser Herausforderungen durch Prozessstandardisierung, Automatisierung und optimiertes Ertragsmanagement ist entscheidend für die Kostensenkung und die Steigerung der Akzeptanz. Unternehmen wie Intel, Samsung und ASE investieren in optimierte Fertigungstechniken und KI-gestützte Designwerkzeuge, um diese Hürden zu überwinden.

- Hochwertige 3D-Gehäuse bieten zwar deutliche Leistungsvorteile, ihre hohen Kosten können jedoch für preissensible Märkte oder margenschwache Anwendungen in der Unterhaltungselektronik ein Hindernis darstellen. Einfache Gehäuselösungen sind weiterhin wirtschaftlicher, erfüllen aber nicht die Leistungsanforderungen von KI- und HPC-Geräten der nächsten Generation.

- Die Bewältigung dieser Herausforderungen durch kosteneffiziente Fertigungsinnovationen, fertigungsgerechte Konstruktionsstrategien und eine breitere Zusammenarbeit der Branche wird für ein nachhaltiges Wachstum des Marktes für 3D-Halbleitergehäuse von entscheidender Bedeutung sein.

Umfang des globalen Marktes für 3D-Halbleiterverpackungen

Der Markt für 3D-Halbleitergehäuse ist nach Technologie, Material und Branchensegment unterteilt.

- Durch Technologie

Basierend auf der Technologie ist der globale Markt für 3D-Halbleitergehäuse in 3D Through-Silicon Via (TSV), 3D Package-on-Package (PoP), 3D Fan-Out und 3D Wire Bonding unterteilt. Das 3D-TSV-Segment dominierte den Markt mit einem Umsatzanteil von 45,6 % im Jahr 2025. Dies ist auf die Fähigkeit der Technologie zurückzuführen, hochdichte Verbindungen, überlegene thermische Leistung und verbesserte Signalintegrität für Hochleistungsrechner, KI und Speicheranwendungen zu ermöglichen. Die TSV-Technologie wird aufgrund ihrer fortschrittlichen Logik-Speicher-Integration bevorzugt eingesetzt und bietet Skalierbarkeit für Halbleiterdesigns der nächsten Generation.

Das Segment der 3D-Fan-Out-basierten Technologie wird voraussichtlich von 2026 bis 2033 mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 22,1 % das schnellste Wachstum verzeichnen. Treiber dieser Entwicklung ist die steigende Nachfrage nach kompakter, leistungsstarker Mobil- und Unterhaltungselektronik. Zu den Vorteilen zählen die reduzierte Gehäusegröße, die höhere I/O-Dichte und die verbesserte Energieeffizienz. Damit ist diese Technologie eine ideale Lösung für Smartphones, IoT-Geräte und Wearables, bei denen optimale Platznutzung und effizientes Wärmemanagement entscheidend sind.

- Nach Material

Basierend auf dem Material ist der globale Markt für 3D-Halbleitergehäuse in organische Substrate, Bonddrähte, Leadframes, Vergussmassen, Keramikgehäuse und Chipbefestigungsmaterialien unterteilt. Das Segment der organischen Substrate dominierte den Markt mit einem Umsatzanteil von 41,8 % im Jahr 2025. Dies ist auf seine Kosteneffizienz, mechanische Zuverlässigkeit und Kompatibilität mit fortschrittlichen 3D-Gehäuseverfahren zurückzuführen. Organische Substrate werden aufgrund ihrer Fähigkeit, hochdichte Verbindungen und thermische Stabilität zu unterstützen, häufig in Mobilgeräten, Computern und Unterhaltungselektronik eingesetzt.

Für das Segment der Verkapselungsharze wird von 2026 bis 2033 mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 20,7 % das schnellste Wachstum erwartet. Treiber dieses Wachstums sind der steigende Bedarf an zuverlässigem Schutz gestapelter Chips, verbesserter Wärmeleitfähigkeit und optimierter elektrischer Isolation. Harze ermöglichen zudem robuste Gehäuse für anspruchsvolle Betriebsbedingungen und sind in Anwendungen, die mechanische Integrität erfordern, wie beispielsweise Automobilelektronik und Industriegeräte, unerlässlich.

- Nach Branchensegment

Basierend auf den Branchensegmenten ist der globale Markt für 3D-Halbleitergehäuse in die Bereiche Elektronik, Industrie, Automobil & Transport, Gesundheitswesen, IT & Telekommunikation sowie Luft- und Raumfahrt & Verteidigung unterteilt. Das Elektroniksegment dominierte den Markt mit einem Umsatzanteil von 46,3 % im Jahr 2025. Treiber dieses Wachstums sind die hohe Nachfrage nach Hochleistungsrechnerchips, Mobilgeräten, Speichermodulen und Unterhaltungselektronik, die kompakte, effiziente und thermisch optimierte Gehäuselösungen erfordern. Die zunehmende Verbreitung von Smartphones, die Nutzung künstlicher Intelligenz und das Wachstum von IoT-Geräten sind wesentliche Treiber für dieses Segment.

Der Automobil- und Transportsektor wird voraussichtlich von 2026 bis 2033 mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 21,5 % das schnellste Wachstum verzeichnen. Treiber dieser Entwicklung ist der steigende Bedarf an fortschrittlichen Fahrerassistenzsystemen (ADAS), Elektrofahrzeugen und Infotainmentsystemen im Fahrzeug. Diese Anwendungen erfordern robuste Halbleitergehäuse mit hoher Packungsdichte, die auch unter anspruchsvollen thermischen und mechanischen Bedingungen zuverlässig funktionieren.

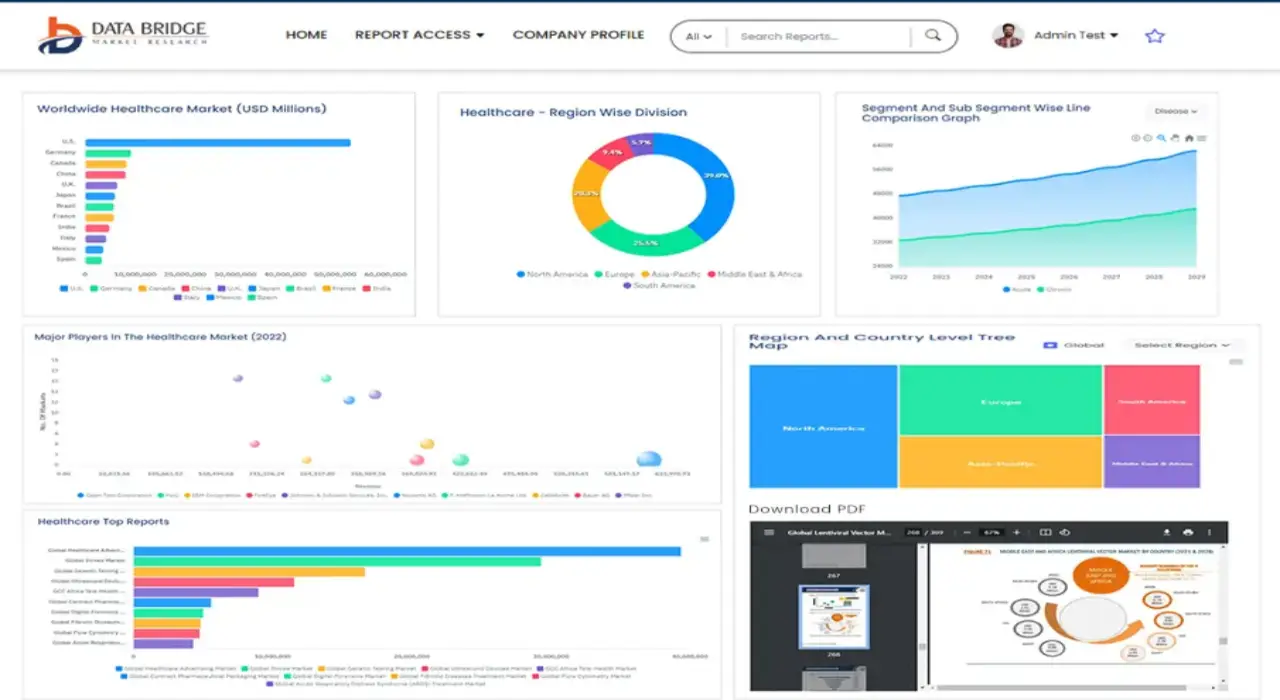

Regionale Analyse des globalen Marktes für 3D-Halbleitergehäuse

- Der asiatisch-pazifische Raum dominierte den globalen Markt für 3D-Halbleiterverpackungen mit dem größten Umsatzanteil von 32,2 % im Jahr 2025. Dies ist auf die starke Präsenz führender Halbleiterhersteller, die frühe Einführung fortschrittlicher Verpackungstechnologien und die hohe Nachfrage nach Hochleistungsrechnern und KI-fähigen Geräten zurückzuführen.

- Unternehmen in der Region, darunter Intel, AMD und GlobalFoundries, investieren massiv in 3D-Packaging-Lösungen wie Through-Silicon Via (TSV), Package-on-Package (PoP) und Fan-Out Wafer-Level Packaging, um den wachsenden Anforderungen von Rechenzentren, Unterhaltungselektronik und Mobilgeräten gerecht zu werden.

- Diese breite Akzeptanz wird durch erhebliche Investitionen in Forschung und Entwicklung, eine robuste Halbleiterinfrastruktur und eine technologieaffine Bevölkerung weiter gefördert, wodurch sich Nordamerika als wichtiger Innovationsstandort für 3D-Halbleitergehäuse etabliert hat. Der Fokus auf Miniaturisierung, verbessertes Wärmemanagement und höhere Bandbreitenleistung treibt das Marktwachstum sowohl im Unternehmens- als auch im Verbraucherbereich weiter an.

Einblick in den US-amerikanischen Markt für 3D-Halbleiterverpackungen

Der US-amerikanische Markt für 3D-Halbleitergehäuse wird 2025 mit 38 % den größten Umsatzanteil in Nordamerika erzielen. Treiber dieses Wachstums sind die Präsenz führender Halbleiterhersteller, die frühzeitige Einführung fortschrittlicher Gehäusetechnologien und die hohe Nachfrage nach Hochleistungsrechnern, KI und Speicheranwendungen. Unternehmen wie Intel, AMD und GlobalFoundries investieren massiv in Through-Silicon-Via- (TSV), Fan-Out-Wafer-Level-Packaging- (F-Out-Wafer-Level-Packaging-) und Package-on-Package- (PoP-) Lösungen, um die Anforderungen in Rechenzentren, Mobilgeräten und Unterhaltungselektronik zu erfüllen. Der zunehmende Fokus auf Miniaturisierung, höhere Bandbreite und verbessertes Wärmemanagement treibt das Marktwachstum weiter an. Darüber hinaus unterstützen das robuste F&E-Ökosystem und die starke Halbleiterinfrastruktur der USA die schnelle Einführung innovativer 3D-Gehäuselösungen in Unternehmens- und Verbraucheranwendungen.

Einblick in den europäischen Markt für 3D-Halbleiterverpackungen

Der europäische Markt für 3D-Halbleitergehäuse wird im Prognosezeitraum voraussichtlich ein deutliches Wachstum verzeichnen. Treiber dieses Wachstums sind strenge Qualitätsstandards, die steigende Nachfrage nach energieeffizienten und kompakten Elektronikgeräten sowie die zunehmende Verbreitung von IoT- und KI-gestützten Anwendungen. Deutschland, Frankreich und die Niederlande tragen aufgrund ihrer starken Kompetenzen in der Elektronik- und Halbleiterfertigung maßgeblich dazu bei. Europäische Hersteller integrieren 3D-Gehäuselösungen, um die Geräteleistung zu optimieren und den Stromverbrauch zu senken. Der Fokus der Region auf nachhaltige und zuverlässige Halbleiterlösungen fördert das Wachstum in den Bereichen Industrie, Automobil und Unterhaltungselektronik.

Einblick in den britischen Markt für 3D-Halbleiterverpackungen

Der britische Markt für 3D-Halbleitergehäuse wird voraussichtlich ein beachtliches jährliches Wachstum verzeichnen, gestützt durch die steigende Nachfrage nach Hochleistungsrechnern, Rechenzentren und KI-Anwendungen. Zunehmende Investitionen in die Elektronikforschung und -entwicklung sowie die Einführung fortschrittlicher Gehäusetechnologien wie TSV und PoP treiben das Marktwachstum an. Darüber hinaus fördern das starke Technologie-Ökosystem Großbritanniens, der Fokus auf Halbleiterinnovationen und die staatliche Unterstützung der Elektronikfertigung den Einsatz von 3D-Gehäuselösungen in kommerziellen und industriellen Anwendungen.

Einblick in den deutschen Markt für 3D-Halbleiterverpackungen

Der deutsche Markt für 3D-Halbleitergehäuse wird voraussichtlich ein beachtliches Wachstum verzeichnen, angetrieben durch die steigende Nachfrage nach Automobilelektronik, Industrieautomation und IoT-Geräten. Deutschlands etablierte Halbleiterinfrastruktur und der Fokus auf Präzisionstechnik fördern die Einführung hochzuverlässiger 3D-Gehäusetechnologien. Zu den wichtigsten Treibern zählen strenge Qualitätsstandards, die Präferenz für energieeffiziente und kompakte Elektroniksysteme sowie die Integration von 3D-Gehäusen in fortschrittliche Automobil- und Industrieanwendungen. Die Region setzt weiterhin auf Innovationen in den Bereichen Wärmemanagement, Miniaturisierung und hochdichte Verbindungslösungen.

Einblick in den asiatisch-pazifischen Markt für 3D-Halbleiterverpackungen

Der Markt für 3D-Halbleitergehäuse im asiatisch-pazifischen Raum wird voraussichtlich im Zeitraum 2026–2033 mit einer jährlichen Wachstumsrate (CAGR) von 23 % am schnellsten wachsen. Treiber dieses Wachstums sind die rasante Urbanisierung, steigende verfügbare Einkommen und die starke Elektronik- und Halbleiterfertigung in Ländern wie China, Japan, Südkorea und Taiwan. Die Region ist ein bedeutendes Zentrum für die Produktion von Speichern, Mobilgeräten und Unterhaltungselektronik, und 3D-Gehäuselösungen werden zunehmend für leistungsstarke und kompakte Geräte eingesetzt. Staatliche Initiativen zur Förderung von Forschung und Entwicklung im Halbleiterbereich sowie der lokalen Fertigung beschleunigen das Marktwachstum zusätzlich. Auch die Präsenz von Branchengrößen wie TSMC, Samsung und ASE trägt dazu bei.

Einblick in den japanischen Markt für 3D-Halbleiterverpackungen

Der japanische Markt für 3D-Halbleitergehäuse gewinnt aufgrund des Fokus des Landes auf fortschrittliche Elektronik, Robotik und KI-Technologien zunehmend an Dynamik. Die rasante Verbreitung von Hochleistungsrechnern und IoT-Geräten treibt die Nachfrage nach miniaturisierten und thermisch effizienten 3D-Gehäuselösungen an. Japanische Hersteller legen Wert auf Qualität, Zuverlässigkeit und Energieeffizienz und fördern so die Integration von TSV-, Fan-Out- und PoP-Technologien in Unterhaltungselektronik, Automobilindustrie und Industrieanwendungen. Der Markt wird zudem durch eine starke F&E-Infrastruktur und staatliche Initiativen zur Förderung von Halbleiterinnovationen unterstützt.

Einblick in den chinesischen Markt für 3D-Halbleiterverpackungen

Der chinesische Markt für 3D-Halbleitergehäuse wird 2025 den größten Marktanteil im asiatisch-pazifischen Raum erzielen. Treiber dieses Wachstums sind die rasante Urbanisierung, die wachsende Elektronikfertigung und die steigende Inlandsnachfrage nach Smartphones, KI-Chips und Speicherbausteinen. Chinas Fokus auf den Aufbau eines autarken Halbleiter-Ökosystems, verbunden mit staatlichen Förderprogrammen für fortschrittliche Gehäusetechnologien und dem Ausbau lokaler Produktionskapazitäten, treibt die Verbreitung von TSV-, Fan-Out- und PoP-Lösungen voran. Die kostengünstige Produktion in Kombination mit der hohen Nachfrage nach Konsum- und Industrieelektronik macht China zu einem Schlüsselmarkt für 3D-Halbleitergehäuse in der APAC-Region.

Weltweiter Marktanteil für 3D-Halbleiterverpackungen

Die 3D-Halbleiterverpackungsindustrie wird hauptsächlich von etablierten Unternehmen dominiert, darunter:

• Intel Corporation (USA)

• TSMC – Taiwan Semiconductor Manufacturing Company (Taiwan)

• Samsung Electronics (Südkorea)

• ASE Technology Holding Co., Ltd. (Taiwan)

• Amkor Technology, Inc. (USA)

• JEDEC Solid State Technology Association Members (USA)

• GlobalFoundries (USA)

• STMicroelectronics (Schweiz)

• NXP Semiconductors (Niederlande)

• Hynix Semiconductor (Südkorea)

• Cadence Design Systems (USA)

• Micron Technology (USA)

• On Semiconductor (USA)

• Siliconware Precision Industries Co., Ltd. (SPIL) (Taiwan)

• JEOL Ltd. (Japan)

• Powertech Technology Inc. (PTI) (Taiwan)

• Taiyo Yuden Co., Ltd. (Japan)

• ChipMOS Technologies Inc. (Taiwan)

• Unimicron Technology Corporation (Taiwan)

• Advanced Micro Devices, Inc. (AMD) (USA)

Welche aktuellen Entwicklungen gibt es auf dem globalen Markt für 3D-Halbleitergehäuse?

- Im April 2024 kündigte die Intel Corporation, ein weltweit führender Halbleiterhersteller, den Start ihres Pilotprogramms für fortschrittliches 3D-Packaging in Arizona, USA, an. Ziel des Programms ist die Verbesserung der Leistung von High-Performance-Computing- (HPC) und KI-Chips. Diese Initiative unterstreicht Intels Engagement für die Entwicklung modernster 3D-Through-Silicon-Via- (TSV) und Package-on-Package- (PoP) Technologien, die der wachsenden Nachfrage nach miniaturisierten Halbleiterlösungen mit hoher Bandbreite gerecht werden. Durch die Nutzung seiner globalen Expertise und innovativen Packaging-Methoden stärkt Intel seine Führungsposition im schnell wachsenden globalen Markt für 3D-Halbleiter-Packaging.

- Im März 2024 stellte TSMC (Taiwan Semiconductor Manufacturing Company) seine neue 3D-Fan-Out-Wafer-Level-Packaging-Plattform vor, die speziell für KI-Prozessoren und mobile Geräte entwickelt wurde. Diese fortschrittliche Packaging-Lösung ermöglicht eine höhere Verbindungsdichte, verbesserte Wärmeableitung und einen geringeren Stromverbrauch. TSMCs Innovation unterstreicht das Bestreben des Unternehmens, kleinere, schnellere und energieeffizientere Halbleiter für die globale Elektronik- und Automobilindustrie zu entwickeln.

- Im März 2024 nahm Samsung Electronics in seinem neuen Werk in Pyeongtaek seine fortschrittlichen 3D-Packaging-Lösungen für Speicherchips der nächsten Generation in Betrieb, um die Produktion für KI-, Rechenzentrums- und mobile Anwendungen zu steigern. Diese Initiative unterstreicht Samsungs Engagement für die Nutzung hochdichter 3D-Packaging-Technologien wie TSV und Fan-Out, um die weltweit wachsende Nachfrage nach kompakten und leistungsstarken Geräten zu decken.

- Im Februar 2024 gab ASE Technology Holding Co., Ltd., ein führender Anbieter von Lösungen für die Halbleitermontage und -prüfung, eine strategische Zusammenarbeit mit einem europäischen Automobilhersteller bekannt. Ziel der Kooperation ist die Integration von 3D-Package-on-Package-Lösungen (PoP) für fortschrittliche Fahrerassistenzsysteme (ADAS). Diese Partnerschaft unterstreicht ASEs Fokus auf die Verbesserung von Leistung, Zuverlässigkeit und thermischer Effizienz von Automobilelektronik und trägt damit der steigenden Nachfrage nach intelligenten und vernetzten Fahrzeugen Rechnung.

- Im Januar 2024 präsentierte Amkor Technology, Inc. auf der SEMICON West 2024 ihre 3D-Drahtbond-Gehäuselösung der nächsten Generation. Diese wurde für Hochgeschwindigkeits- und Hochdichte-Halbleiteranwendungen in der Unterhaltungselektronik und in industriellen Geräten entwickelt. Die innovative Gehäuseplattform unterstreicht Amkors Engagement für kompakte, kostengünstige und leistungsoptimierte 3D-Halbleiterlösungen und festigt seine Position als weltweit führender Anbieter fortschrittlicher Gehäusetechnologien.

SKU-

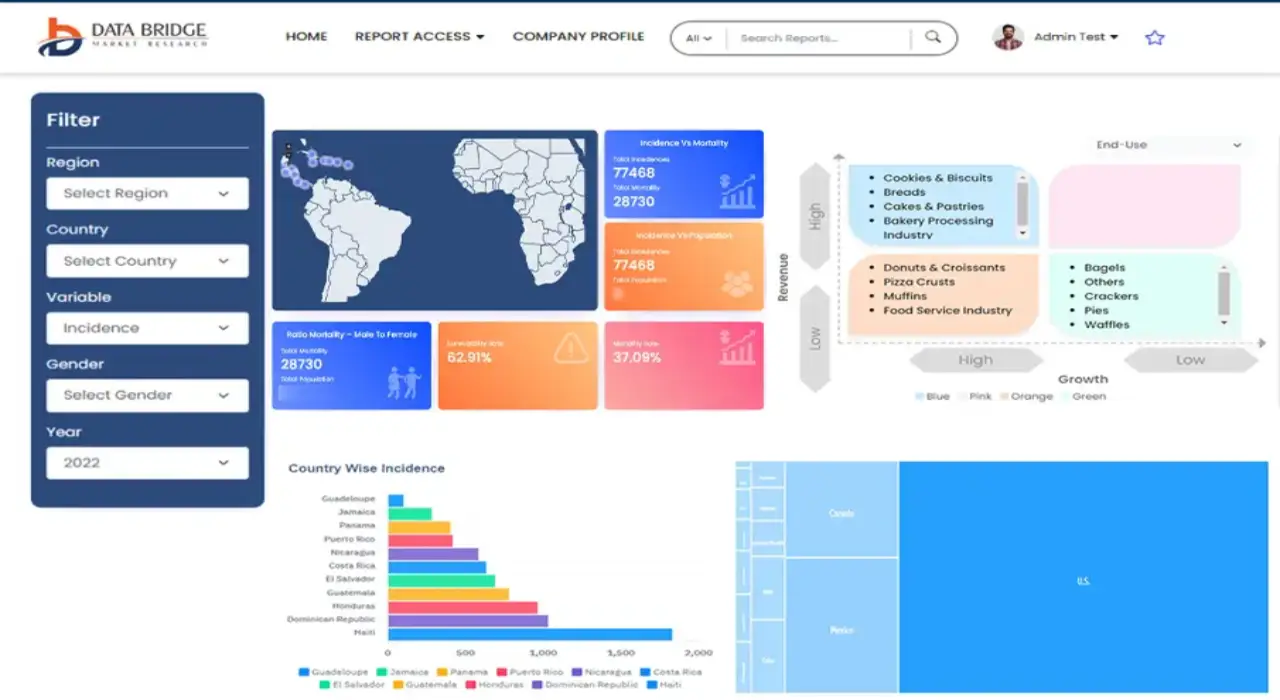

Erhalten Sie Online-Zugriff auf den Bericht zur weltweit ersten Market Intelligence Cloud

- Interaktives Datenanalyse-Dashboard

- Unternehmensanalyse-Dashboard für Chancen mit hohem Wachstumspotenzial

- Zugriff für Research-Analysten für Anpassungen und Abfragen

- Konkurrenzanalyse mit interaktivem Dashboard

- Aktuelle Nachrichten, Updates und Trendanalyse

- Nutzen Sie die Leistungsfähigkeit der Benchmark-Analyse für eine umfassende Konkurrenzverfolgung

Forschungsmethodik

Die Datenerfassung und Basisjahresanalyse werden mithilfe von Datenerfassungsmodulen mit großen Stichprobengrößen durchgeführt. Die Phase umfasst das Erhalten von Marktinformationen oder verwandten Daten aus verschiedenen Quellen und Strategien. Sie umfasst die Prüfung und Planung aller aus der Vergangenheit im Voraus erfassten Daten. Sie umfasst auch die Prüfung von Informationsinkonsistenzen, die in verschiedenen Informationsquellen auftreten. Die Marktdaten werden mithilfe von marktstatistischen und kohärenten Modellen analysiert und geschätzt. Darüber hinaus sind Marktanteilsanalyse und Schlüsseltrendanalyse die wichtigsten Erfolgsfaktoren im Marktbericht. Um mehr zu erfahren, fordern Sie bitte einen Analystenanruf an oder geben Sie Ihre Anfrage ein.

Die wichtigste Forschungsmethodik, die vom DBMR-Forschungsteam verwendet wird, ist die Datentriangulation, die Data Mining, die Analyse der Auswirkungen von Datenvariablen auf den Markt und die primäre (Branchenexperten-)Validierung umfasst. Zu den Datenmodellen gehören ein Lieferantenpositionierungsraster, eine Marktzeitlinienanalyse, ein Marktüberblick und -leitfaden, ein Firmenpositionierungsraster, eine Patentanalyse, eine Preisanalyse, eine Firmenmarktanteilsanalyse, Messstandards, eine globale versus eine regionale und Lieferantenanteilsanalyse. Um mehr über die Forschungsmethodik zu erfahren, senden Sie eine Anfrage an unsere Branchenexperten.

Anpassung möglich

Data Bridge Market Research ist ein führendes Unternehmen in der fortgeschrittenen formativen Forschung. Wir sind stolz darauf, unseren bestehenden und neuen Kunden Daten und Analysen zu bieten, die zu ihren Zielen passen. Der Bericht kann angepasst werden, um Preistrendanalysen von Zielmarken, Marktverständnis für zusätzliche Länder (fordern Sie die Länderliste an), Daten zu klinischen Studienergebnissen, Literaturübersicht, Analysen des Marktes für aufgearbeitete Produkte und Produktbasis einzuschließen. Marktanalysen von Zielkonkurrenten können von technologiebasierten Analysen bis hin zu Marktportfoliostrategien analysiert werden. Wir können so viele Wettbewerber hinzufügen, wie Sie Daten in dem von Ihnen gewünschten Format und Datenstil benötigen. Unser Analystenteam kann Ihnen auch Daten in groben Excel-Rohdateien und Pivot-Tabellen (Fact Book) bereitstellen oder Sie bei der Erstellung von Präsentationen aus den im Bericht verfügbaren Datensätzen unterstützen.